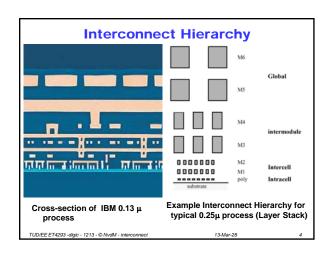

## Outline Capacitance Area/perimeter model, coupling Resistance Sheet resistance Interconnect delay Delay metrics, rc delay, Elmore delay

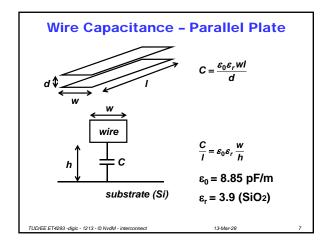

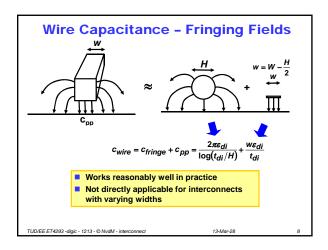

Capacitance

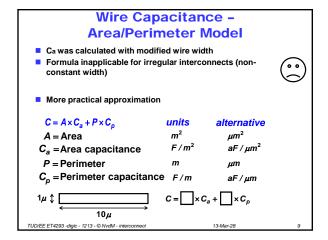

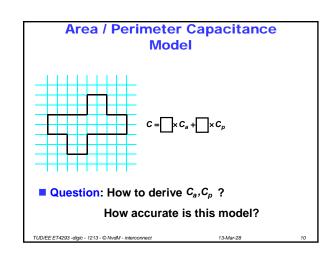

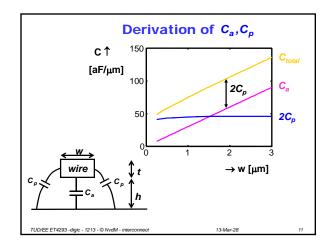

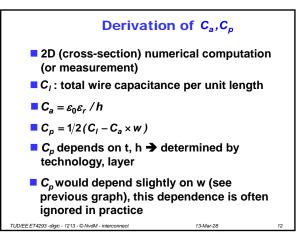

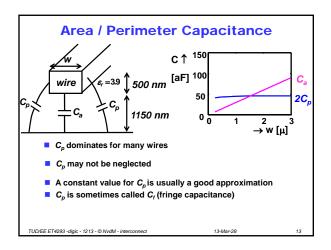

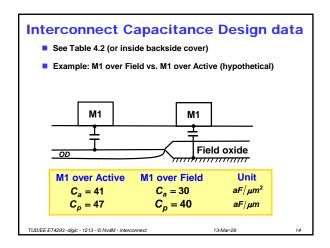

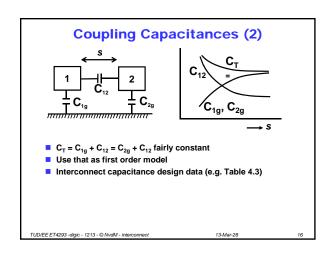

■ Area/perimeter model, coupling

TUD/EE ET4293 -digic - 1213 - © NvdM - interconnect 13-4Mar-28 6

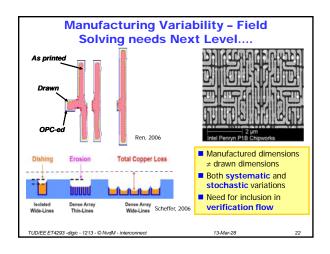

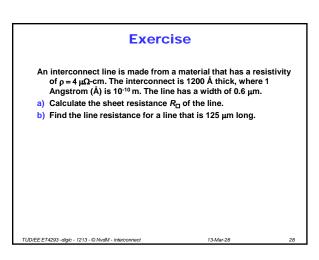

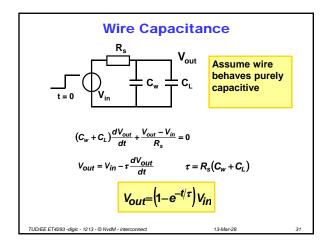

## Wire Resistance Proportional to I Inversely proportional to w and t (cross-sectional area) Proportional to ρ: specific resistance, material property [Ωm] R = ρl/wt Aluminum: ρ = 2.7x10-8 Ωm Copper: ρ = 1.7x10-8 Ωm

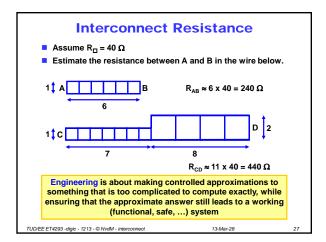

## Sheet Resistance R = ρl/wt t, ρ constant for layer, technology R = Rl/w R: sheet resistance [Ω/] resistance of a square piece of interconnect other symbol: R<sub>s</sub> Interconnect resistance design data e.g. Table 4.5 (or inside back-cover)

TUD/EE ET4293 -digic - 1213 - © NvdM - interconnect

TUD/EE ET4293 -digic - 1213 - © NvdM - interconnect

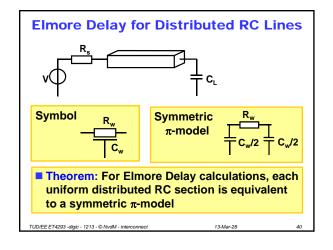

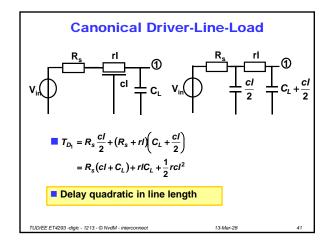

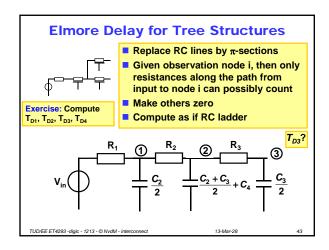

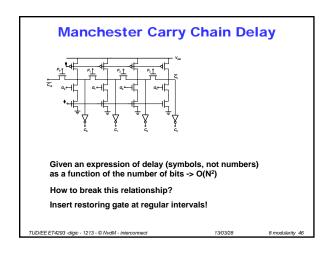

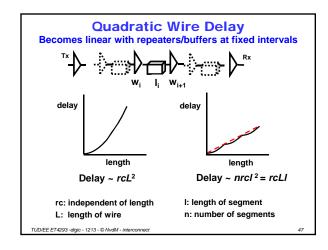

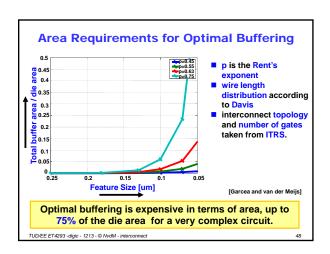

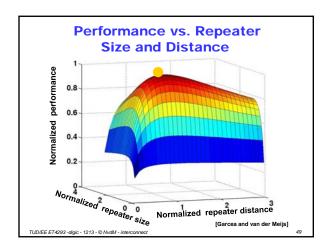

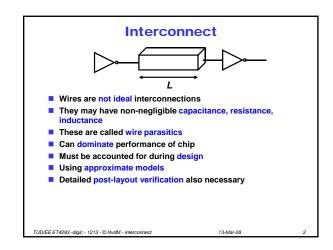

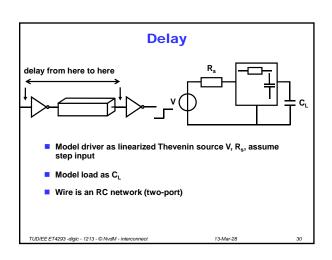

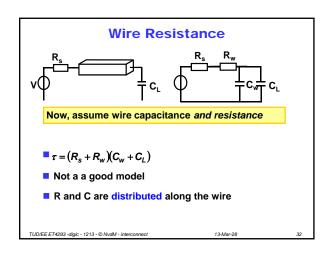

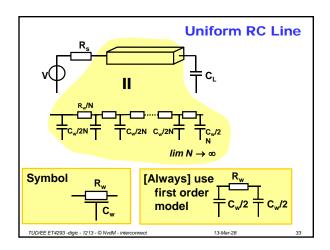

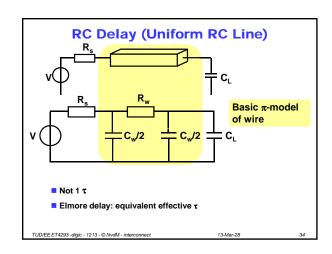

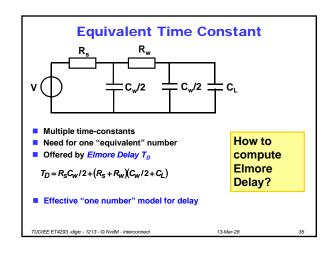

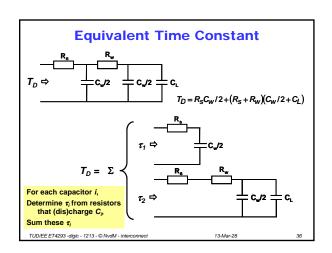

Interconnect delay

■ Delay metrics, rc delay, Elmore delay

TUD/EE ET4293 - digic - 1213 - © NvdM - interconnect 13-Mar-28 29

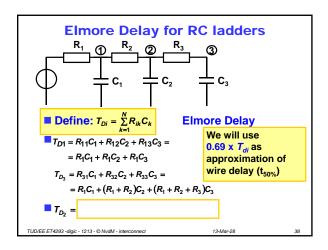

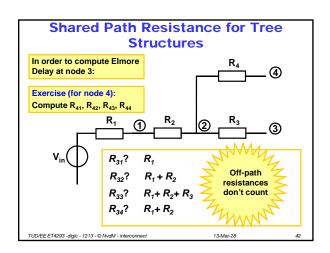

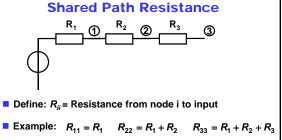

- Define: R<sub>ik</sub> = Shared path resistance to input for node i and k

- $R_{12} = R_1 \quad R_{13} = R_1 \quad R_{23} =$

TUD/EE ET4293 -digic - 1213 - © NvdM - interconnect

13-Mar-28