MODULE 6

TIMING DESIGN

TUDEE ET 1293 - digic - 1213 - © NvdM 06 Timing

TUDEE ET 1293 - digic - 1213 - © NvdM 06 Timing

# Correct signal Logic value Right level (restoring logic, ...) At right place Interconnect (R, C, L) Busses Off-chip drivers, and receivers At right time How to cope with (uncertain) delay

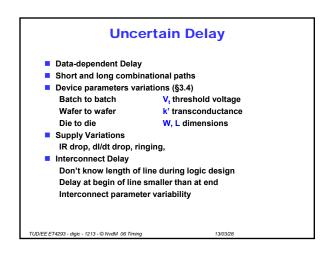

# **Impact of Uncertain Delay**

- Combinational circuits will eventually settle at correct output values when inputs are stable

- Sequential circuits

- Have state

- Must guarantee storing of correct signals at correct time

- Require ordered computations

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

13/03/28

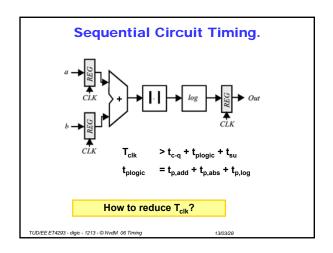

# **Sequential Circuits**

- Sequential circuits require ordered computation

- Several ways for imposing ordering

- √ Synchronous (clock)

- **X** Asynchronous (unstructured)

- X Self-timed (negotiation)

- Clock works like an

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

13/03/28

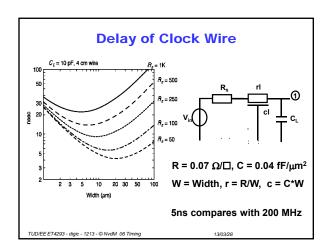

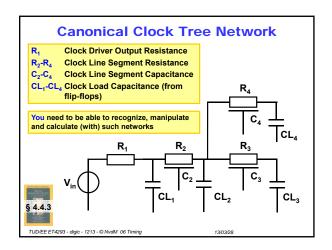

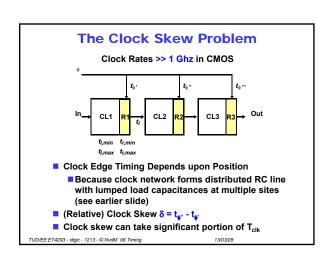

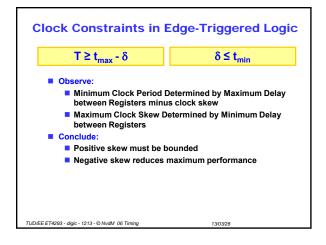

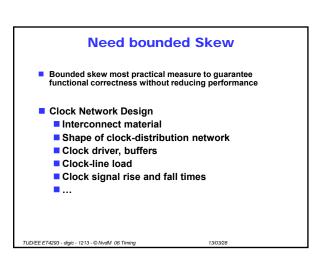

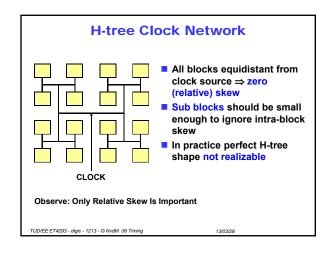

# **Synchronous Design**

- Global Clock Signal

- Synchronicity may be defeated by

- Delay uncertainty in clock signal

- Relative timing errors: clock skew

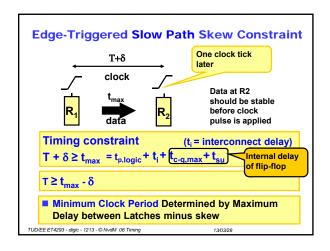

- Slow logic paths

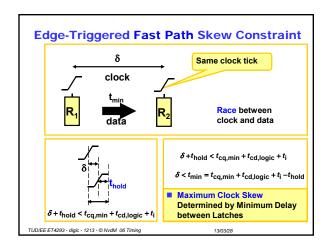

- Fast logic paths

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

12/02/08

## **Timing Design**

- Clocking Scheme is important design decision

- Influences

- Power

- Robustness

- Ease of design, design time

- Performance

- Area, shape of floor plan

- Needs to be planned early in design phase

- But is becoming design bottle neck nevertheless

- Clock frequencies increase

- Die sizes increase

- Clock skew significant fraction of T<sub>clk</sub>

- Alternatives

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

Asynchronous or self-timed

Not in this course

13/03/28

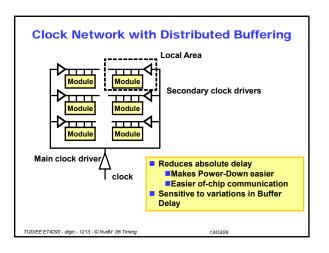

## **More Clocking Issues**

- Clock power (~ 30 % of total chip power)

- Asynchronous design for reasons of power, and variability

- Resonant clocking

Use principles of (buck) convertors

to recycle energy

- Multiple clock domains, power domains, sleep states

- for standby modes

- for integrating IP

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

13/03/2

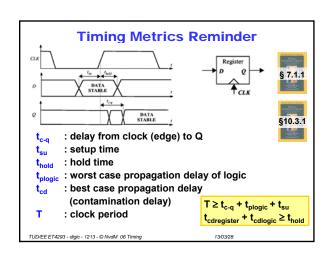

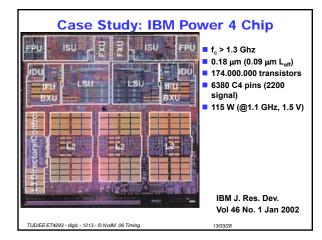

## **Summary**

- Timing Design Background and Motivation

- Delay variations, impact

- Sequential circuits, synchronous design

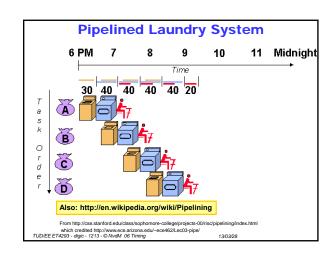

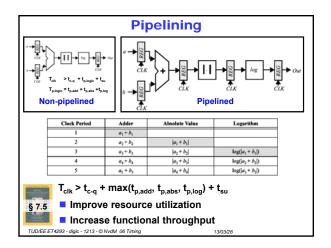

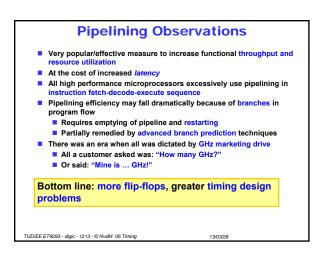

- Pipelining, metrics reminder

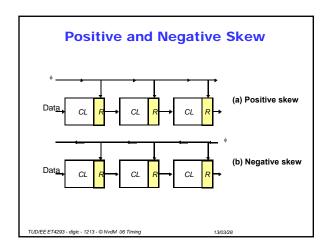

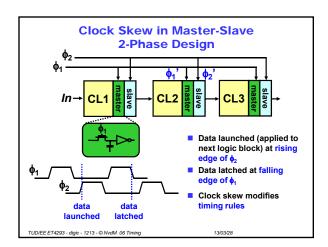

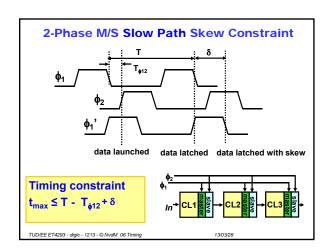

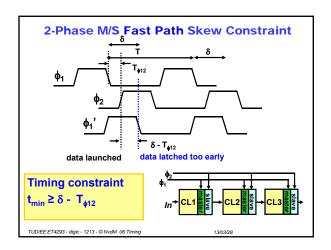

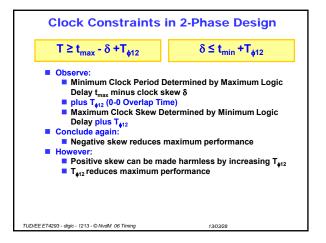

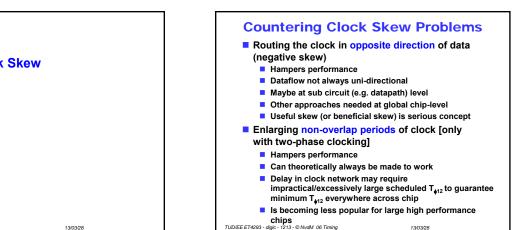

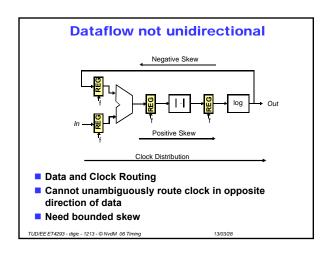

- The Clock Skew Problem

- In single Phase Edge Triggered Clocking

- In Two Phase Master-Slave Clocking

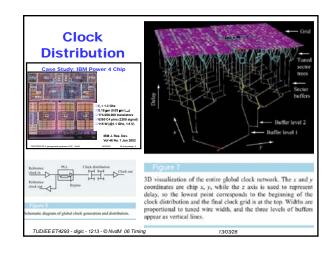

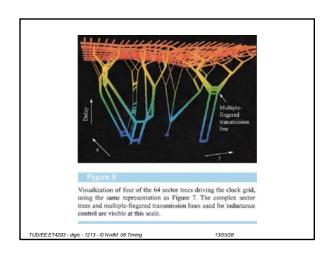

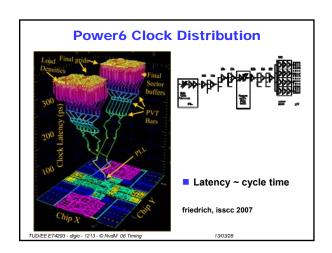

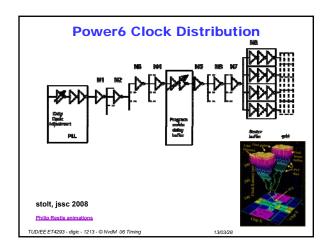

- Controlling Clock Skew

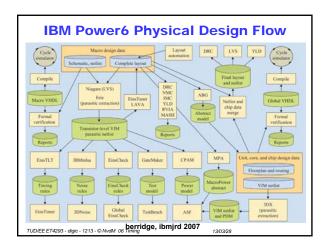

- Case Study

Got basic appreciation of some system level design issues?

TUD/EE ET4293 - digic - 1213 - © NvdM 06 Timing

13/03/28