# MODULE 5 Chapter 7

### **Clocked Storage Elements**

13/03/28

# **Clocked Storage Elements**

#### **Outline**

#### Background

Timing, terminology, classification

#### Static CSEs

- Latches

- Registers

#### Dynamic CSEs

- Latches

- Registers

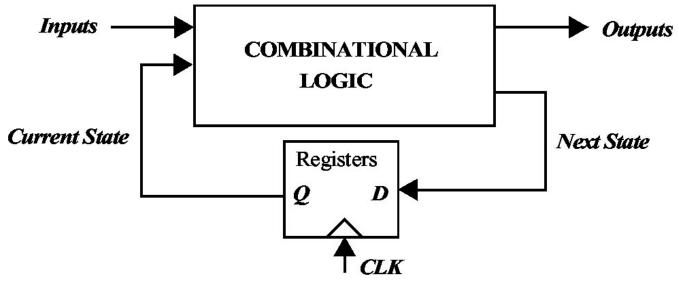

# FSM with Positive Edge Triggered Registers

CSEs/Flip-flops provide memory/state

VLSI uses predominantly D-type flip-flops

## **Memory elements**

- Store a temporary value, remember a state

- Separate the past, current, future

- Typically controlled by clock.

- May have load signal, etc.

- In CMOS, memory is created by:

- capacitance (dynamic);

- feedback (static).

- Also see http://en.wikipedia.org/wiki/Flip-flop\_(electronics)

# Variations in memory elements

- Form of required clock signal.

- How behavior of data input around clock affects the stored value.

- When the stored value is presented to the output.

- Whether there is ever a combinational path from input to output.

- Noise sensitivity on input and output

. . .

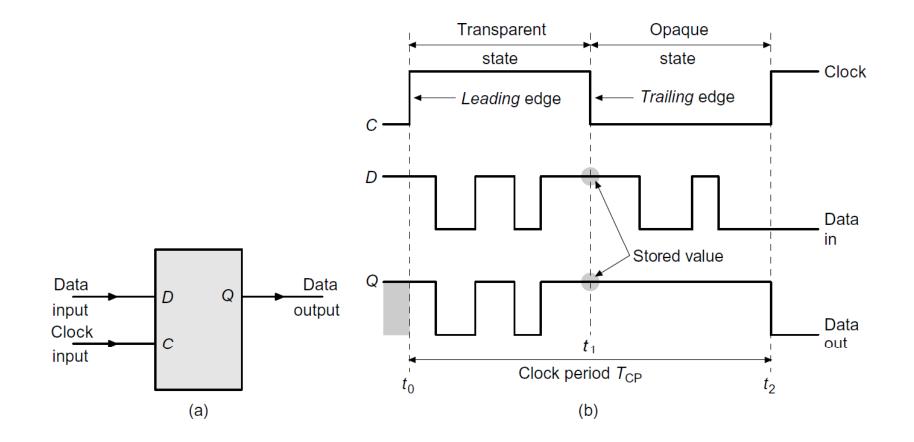

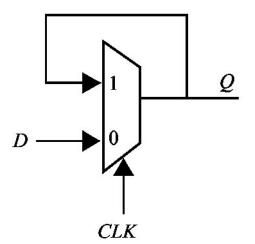

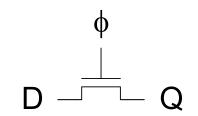

# **D-Latch**

[Taskin, Kourtev & Friedman, The VLSI Handbook]

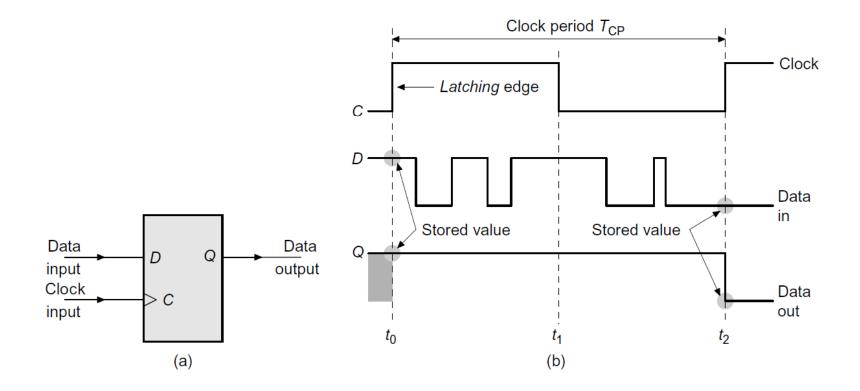

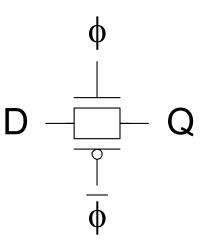

### **D-Register**

#### (more commonly known as D-Flip-Flop)

[Taskin, Kourtev & Friedman, The VLSI Handbook]

## Latches vs. Registers

**Terminology of book**

### Latch

#### Level-sensitive

Transparent when clock is active

Clock active high: positive latch

Clock active low: negative latch

**Faster**, smaller

# Register

#### **Edge-triggered**

Input and output isolated

Sampling on  $0 \rightarrow 1$  clock: positive edge triggered

Sampling on  $1 \rightarrow 0$  clock: negative edge triggered

Safer

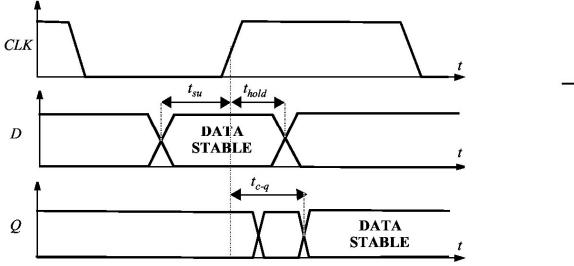

# **Timing Metrics Reminder**

- : delay from clock (edge) to Q

- : setup time

- t<sub>hold</sub>

t<sub>c-q</sub>

t<sub>su</sub>

t<sub>cd</sub>

- : hold time

- t<sub>plogic</sub>

- : worst case propagation delay of logic

- : best case propagation delay

(contamination delay)

T : clock period

$$\label{eq:t_c-q} \begin{split} \textbf{T} &\geq \textbf{t}_{c-q} + \textbf{t}_{plogic} + \textbf{t}_{su} \\ \textbf{t}_{cdregister} + \textbf{t}_{cdlogic} \geq \textbf{t}_{hold} \end{split}$$

# **Static vs. Dynamic Memory Elements**

### **Static**

Operate through positive feedback

Preserve state as long as power is on

Can work when clock is off

More robust

## **Dynamic**

**Store charge on** (parasitic) capacitor

Charge leaks away (in milliseconds)

Clock must be kept running (for periodic refresh)

**Faster**, smaller

Static CSEs / Flipflops

Latches

Registers

Large part of literature talks about Clocked Storage Elements Are called Flip-Flops in book

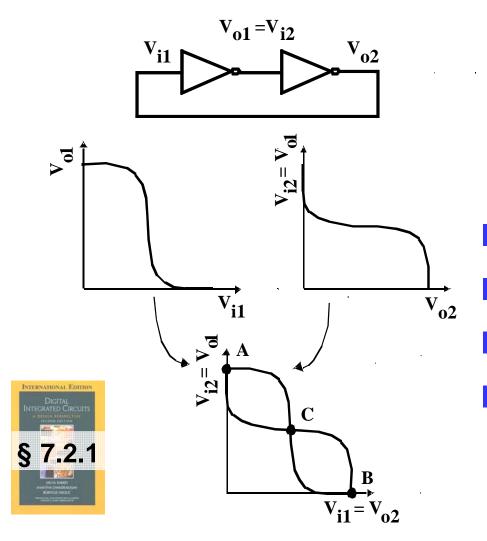

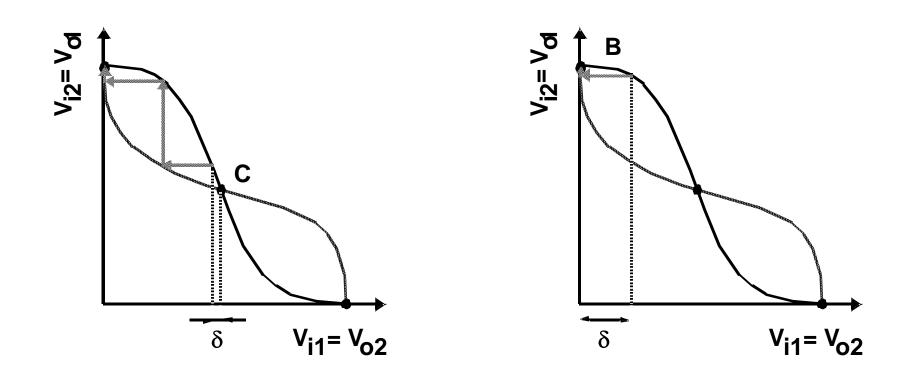

### **Positive Feedback: Bi-Stability**

Loop-gain in A,B <<1</li>

A,B: stable points

Loop-gain in C >> 1

C: meta-stable point

### **Meta-Stability**

# Gain should be larger than 1 in the transition region Smaller than 1 in stable region

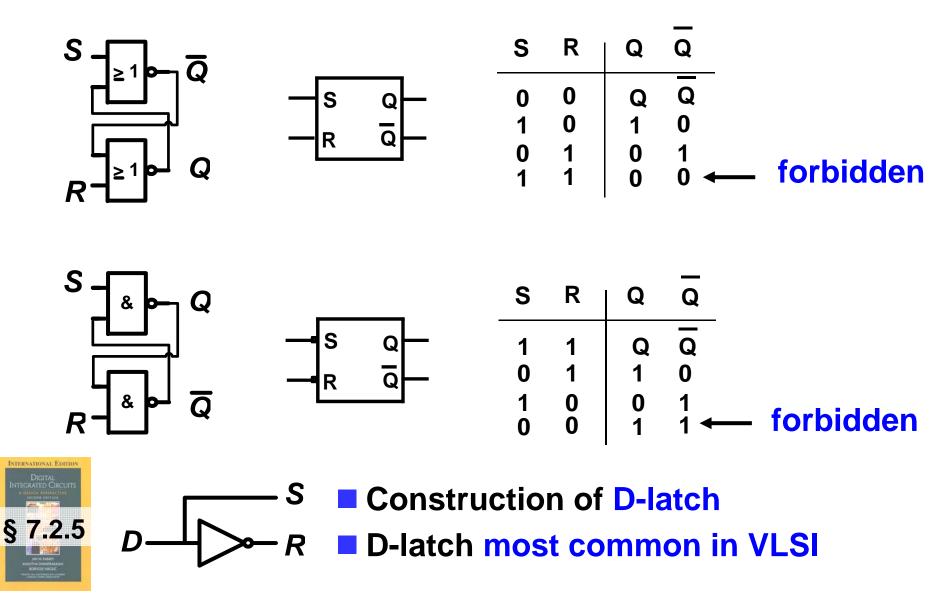

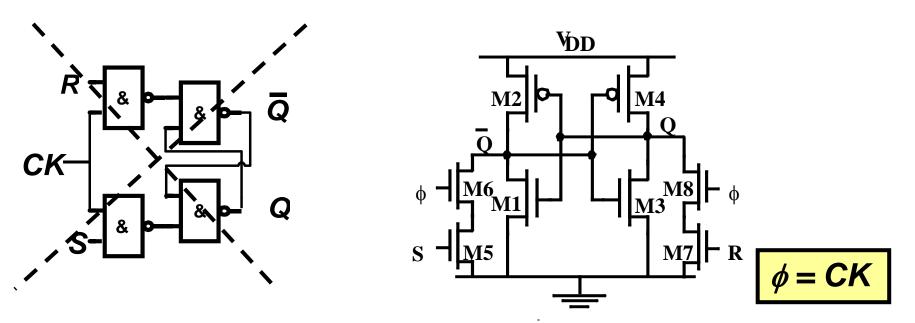

### **SR-Latch**

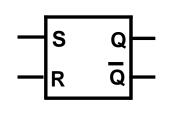

### **Clocked SR-Latch**

- Naïve implementation

- 16 transistors

- D latch requires 9xN, 9xP

- Master-slave D-register needs 18xN, 18xP

- Larger area, cost, power

### **CMOS Clocked SR-Latch**

Save 6 PMOS, 2 NMOS transistors

D-latch requires 7 x N, 3 x P (instead of 9xN, 9xP)

### **{TPS}:** Is this a ratioed design or not? Does it consume static power?

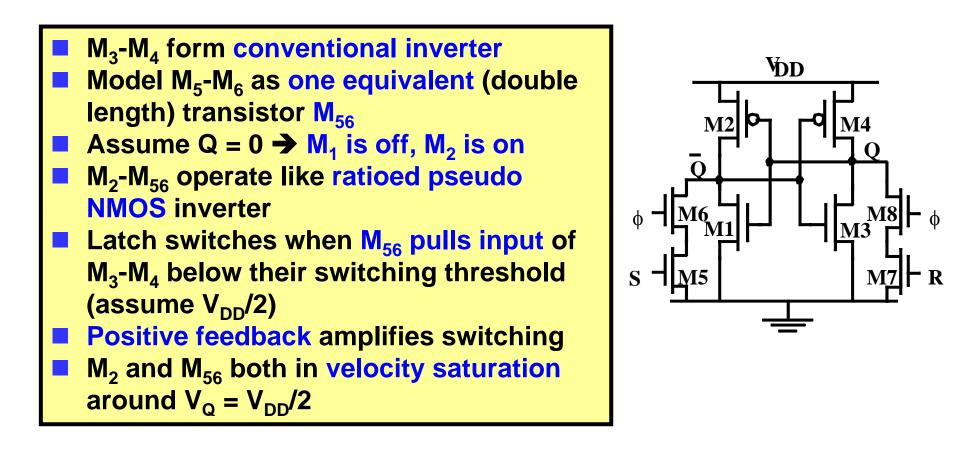

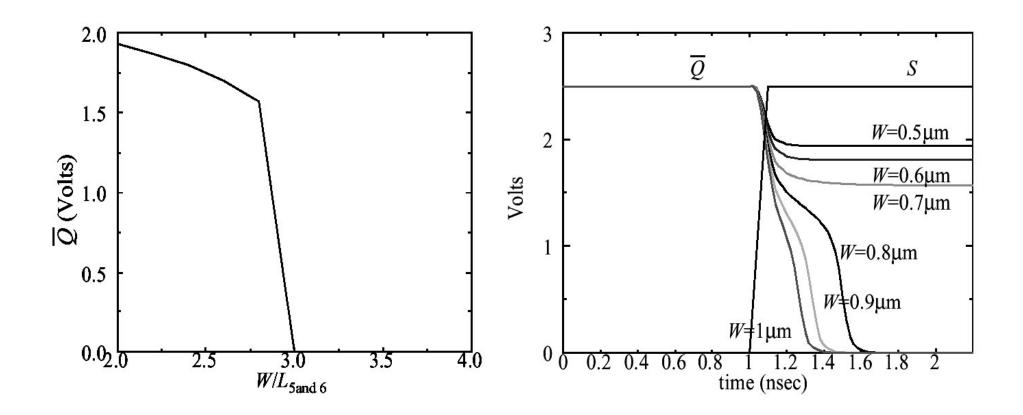

# Sizing for 'Set' Action

$$\boldsymbol{k}_{n}^{'}\left(\frac{W}{L}\right)_{5-6}\left((V_{DD}-V_{Tn})V_{DSATn}-\frac{V_{DSATn}^{2}}{2}\right)=\boldsymbol{k}_{p}^{'}\left(\frac{W}{L}\right)_{2}\left((-V_{DD}-V_{Tp})V_{DSATp}-\frac{V_{DSATp}^{2}}{2}\right)$$

### Sizing for 'Set' Action

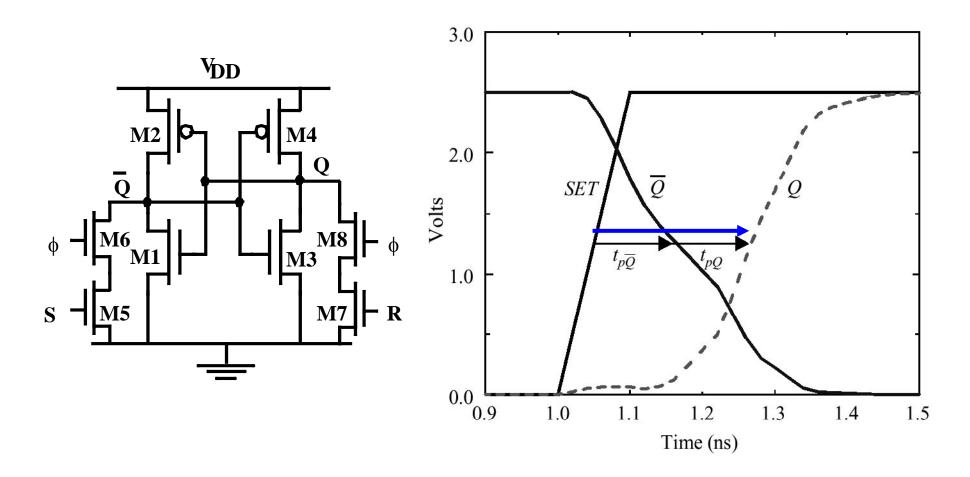

# **SR Latch Timing**

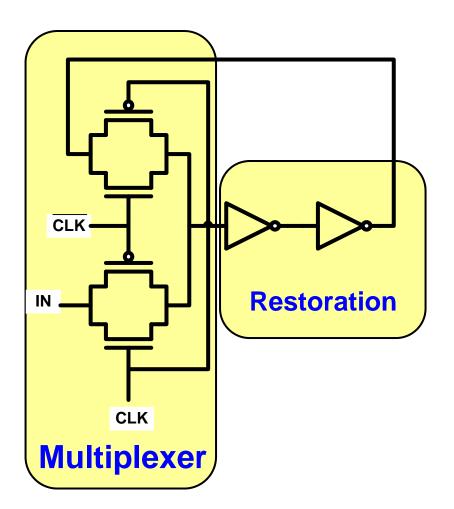

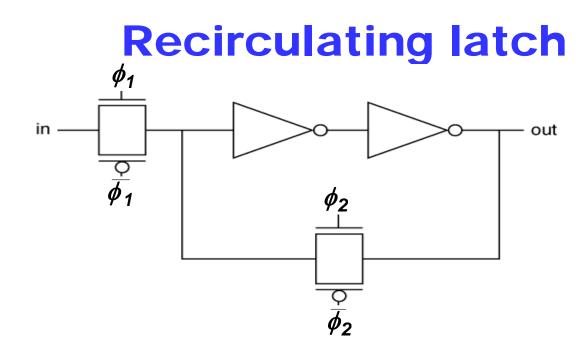

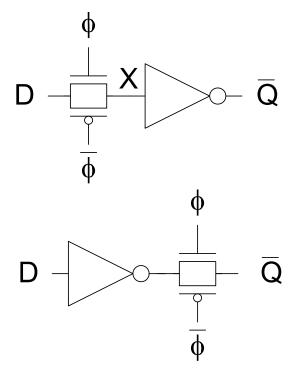

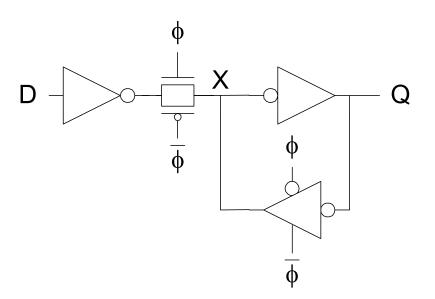

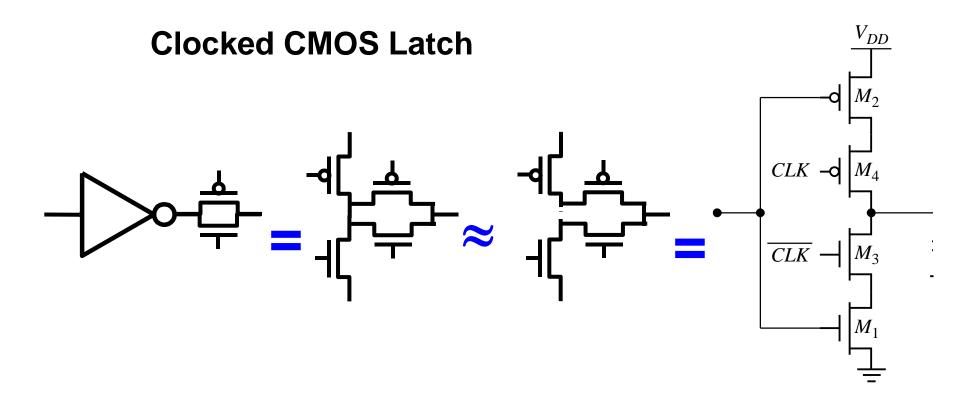

## **Multiplexer-Based Latches**

Negative Latch

Mux-based latches much more common in modern dig. IC's

TUD/EE ET4293 digic 1213 - © NvdM - 05 Sequential

13/03/28

- Quasi-static, static on one phase

- Feedback restores value

- Requires 4 x N, 4 x P, minimum size (compare 7 x N, 3 x P, non-minimum size)

- $\phi_1$  and  $\phi_2$  inverse but should be non-overlapping

- Definitely not ideal, because... {TPS}

#### Let's explore TG/PG based latch designs

#### **Pass Transistor Latch**

- <sup>☉</sup> Tiny

- Low clock load

- 😕 V<sub>t</sub> drop

- e nonrestoring

- Backdriving

- Output noise sensitivity

- 😕 dynamic

- e diffusion input

Used in 1970's

["Latch Design" slides based on Weste & Harris],

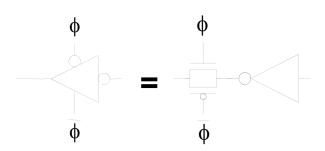

#### Transmission gate ☺ No V<sub>t</sub> drop

Requires inverted clock

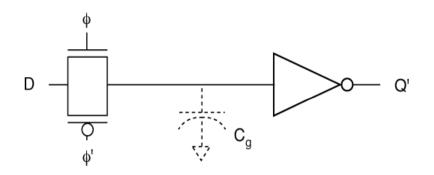

#### **Inverting buffer / Basic Dynamic Latch**

- Restoring

- No backdriving

- Fixes either

- Output noise sensitivity

- Or diffusion input

- Inverted output

## **Dynamic Latch**

- Storage capacitance comes primarily from inverter gate capacitance.

- Setup and hold times determined by transmission gate must ensure that value stored on transmission gate is solid.

- Stored charge leaks away

- Duration of stored value being good depends on technology

- Worst conditions during burn-in (High VDD, high Temp).

- Modern technologies (almost) mandate static latches.

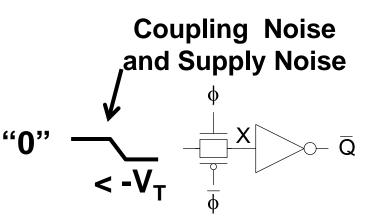

# **Noise Sensitivity**

#### **Diffusion Input Noise Sensitivity**

- Noise on input can drop node below V<sub>T</sub>

- TG NMOS turns on, and X can discharge if it was a "1"

- Similar problems for V<sub>in</sub> > V<sub>DD</sub>

#### **Output Noise Sensitivity**

- State node X is exposed

- Noise spike on output can corrupt the state

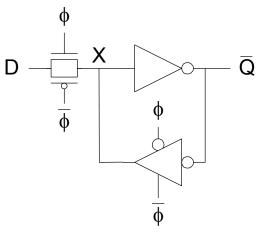

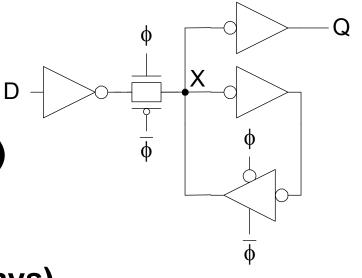

#### **Tristate feedback**

- ☺ Static

- Backdriving risk

- Static latches are now essential because of leakage

- If only during burn-in (@ high VDD, T)

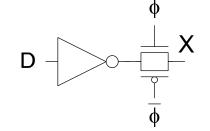

#### **Buffered input**

- **©** Fixes diffusion input

- Oninverting

#### **Buffered output**

Widely used in standard cells

- No backdriving

- Very robust (most important)

- 😕 Rather large

- ⊗ Rather slow (1.5 2 FO4 delays)

- High clock loading

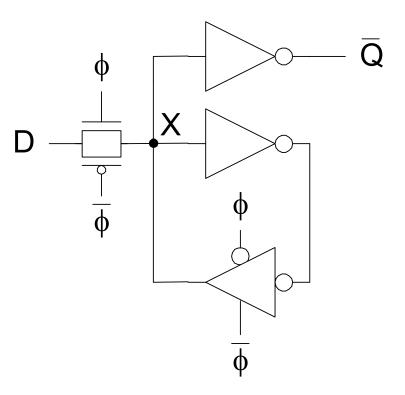

#### **Datapath latch**

(only use in noise-controlled environments)

<sup>☉</sup> Smaller

☺ Faster

Onbuffered input

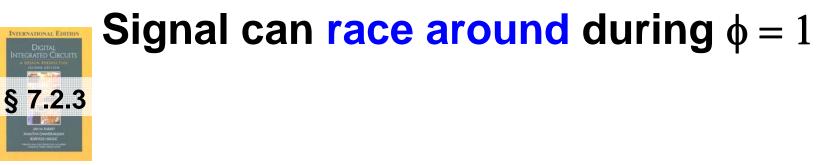

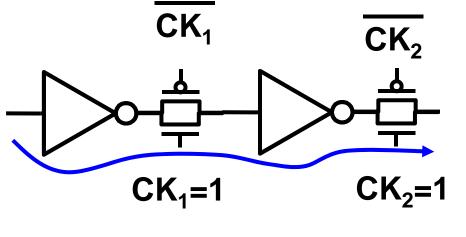

# Latch Designs can Suffer from Race Problems

TUD/EE ET4293 digic 1213 - © NvdM - 05 Sequential

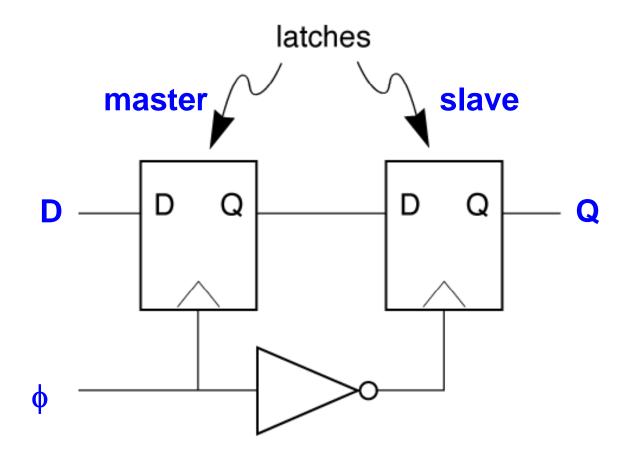

# **Registers**

- Not transparent—use multiple storage elements to isolate output from input.

- Master-slave, edge triggered principle

### **Master-slave operation**

**φ** = **0**:

- master latch is disabled;

- slave latch is enabled,

- but master latch output is stable,

- so output does not change.

$\phi = 1$ :

- master latch is enabled,

- Ioading value from input;

- slave latch is disabled,

- maintaining old output value.

$\phi = \mathbf{1} \rightarrow \mathbf{0}$ :

Slave latch copies current value of master, and master stops changing

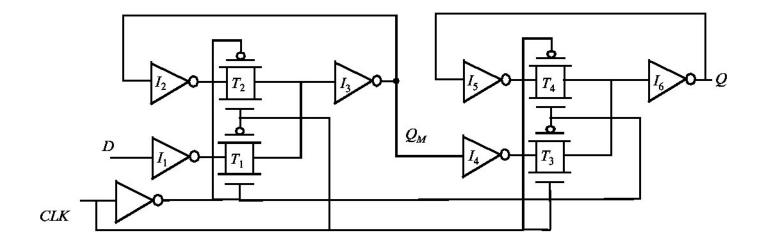

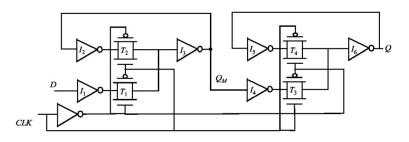

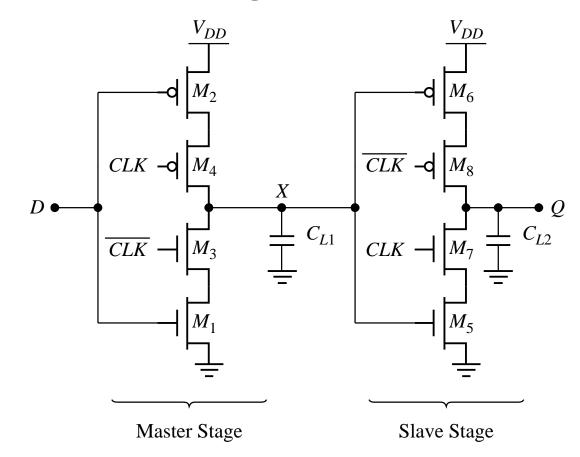

# **Transistor Level Master Slave Positive Edge Triggered Register**

- Robust Design

- Can eliminate I<sub>1</sub> and I<sub>4</sub>, however, they make design more robust (avoid charge sharing, robust input) (see next)

- High Clock Load (8 x)

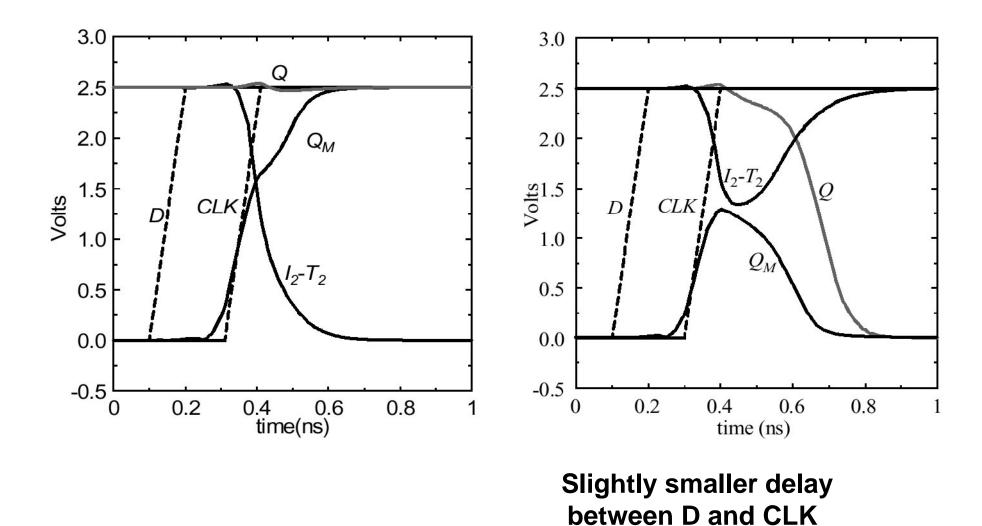

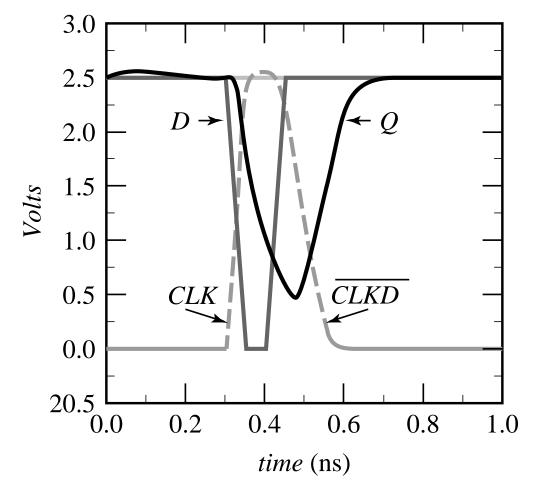

### **Set-up Time Simulation**

# Ratioed Reduced Clock Load Register

- $I_2$  and  $I_4$  are small, even long

- Lower clock load

- Increased design complexity

- Reduced robustness (reverse conduction / backdriving)

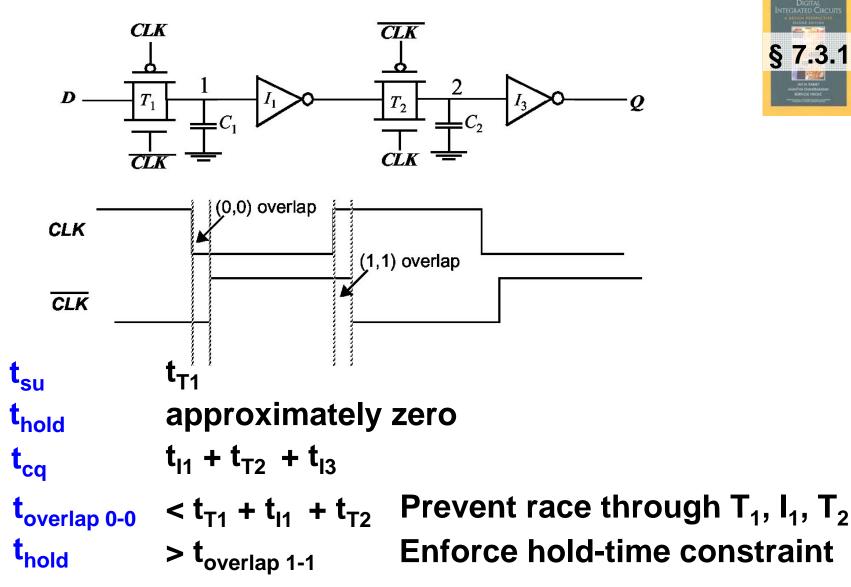

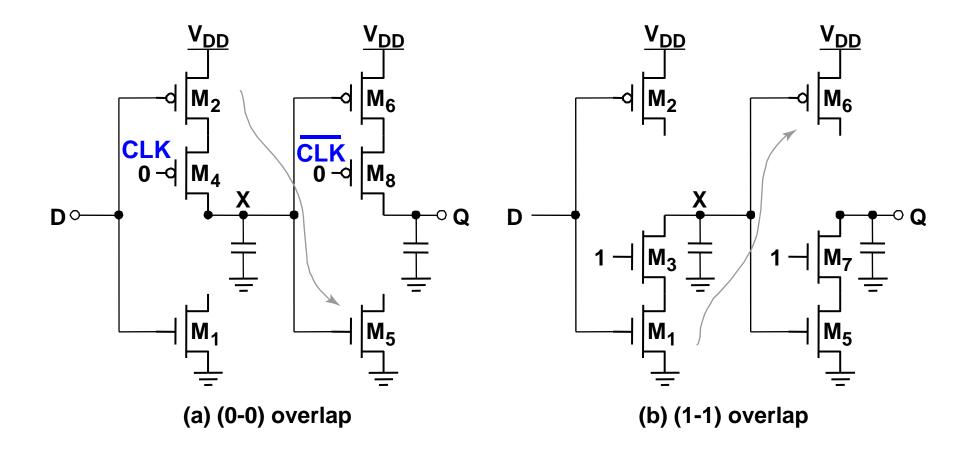

### **Simple Master-Slave Register**

**Clock phase overlap is important design problem**

Similar problem for 0-0 overlap

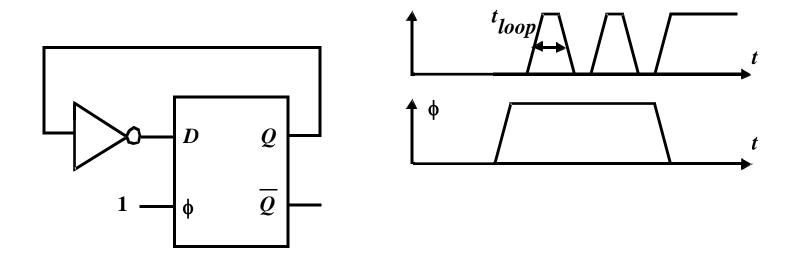

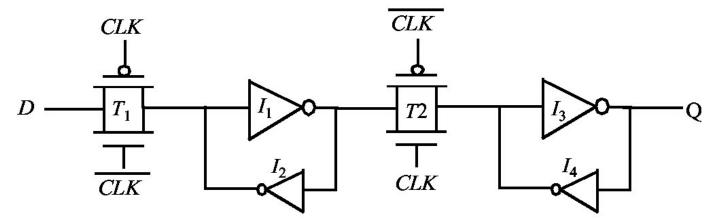

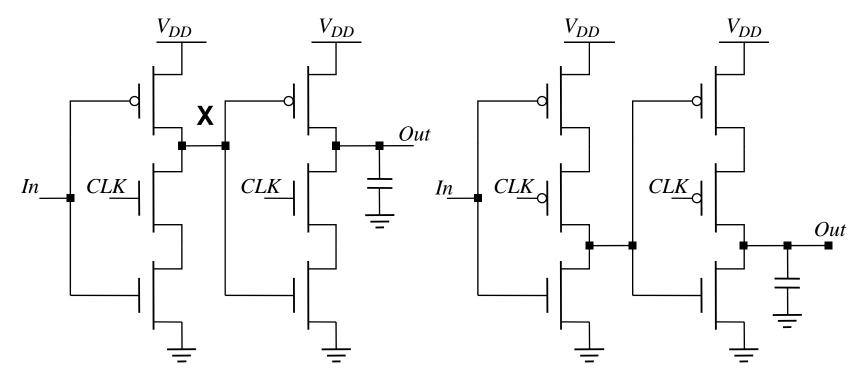

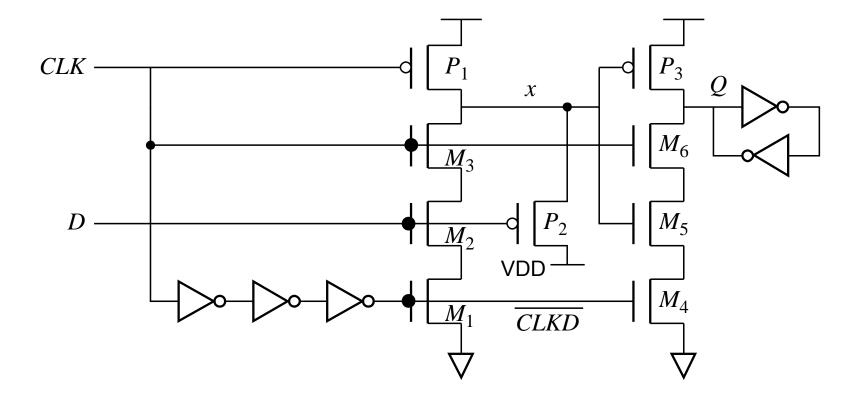

# **Dynamic Edge Triggered Register**

## **Clocking and CSE problems**

- Clock overlap with multiple phases great problem in view of clock skew

- Power in some cases, around 50% of total power

- Delay setup time, clk-to-Q, ...

- Robustness

- Noise-sensitivity of element, specifically for dynamic elements

#### **Next: advanced CSEs to combat some of the above**

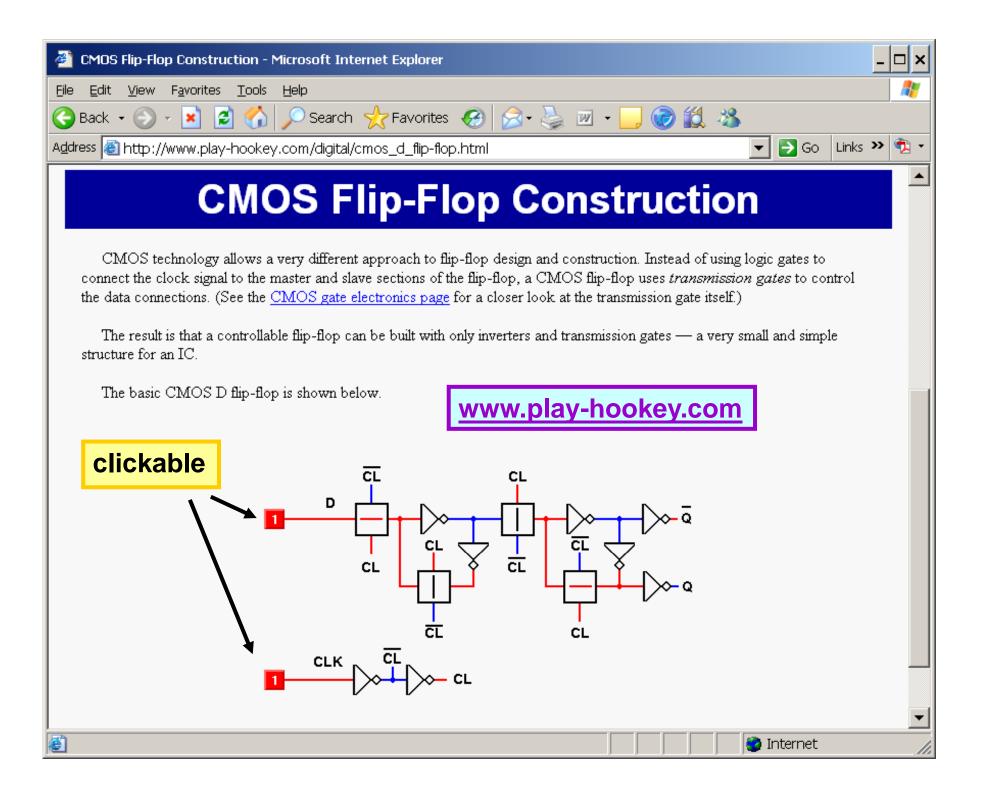

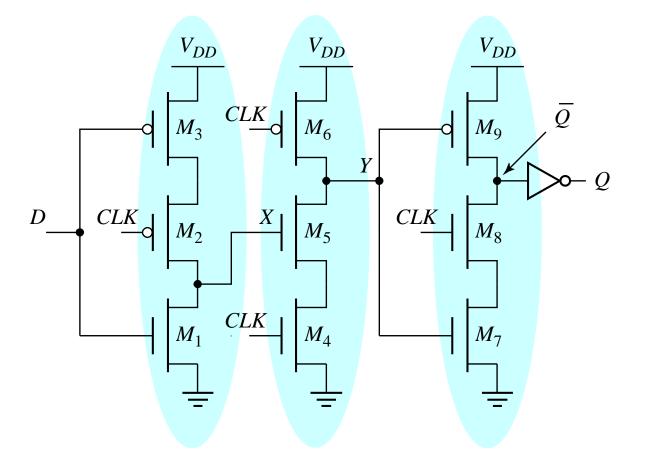

### **Other Latches/Registers: C<sup>2</sup>MOS**

**Clocked CMOS Register – insensitive to overlap**

"Keepers" can be added to make circuit pseudo-static

#### C<sup>2</sup>MOS Latch

Slightly ... Slower Slightly ... Smaller

# **Insensitive to Clock-Overlap**

#### Output always decoupled from input, even with overlap

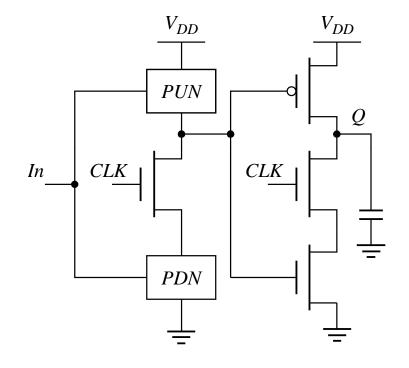

#### **Other Latches/Registers: TSPC**

#### **True Single Phase Clocking**

Positive latch (transparent when CLK= 1) Negative latch (transparent when CLK= 0)

**TSPC** register: positive and negative latch in cascade

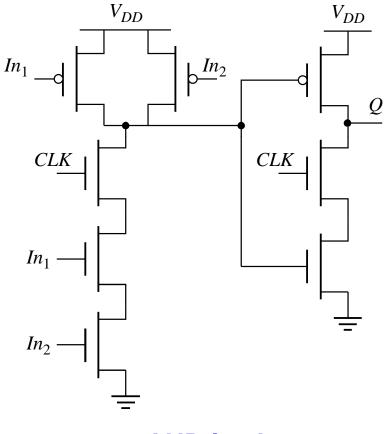

### **Including Logic in TSPC**

#### **Example: logic inside the latch**

**AND latch**

13/03/28

## **Alternative TSPC Register**

| Clk = 0 | D sampled on X           | Precharge Y to VDD  | $Y \uparrow$ doesn't make Q' $\downarrow$ |

|---------|--------------------------|---------------------|-------------------------------------------|

| Clk ↑   |                          | Evaluate based on X |                                           |

| Clk = 1 | Falling X can't charge Y | Y is stable         | Y sampled on Q                            |

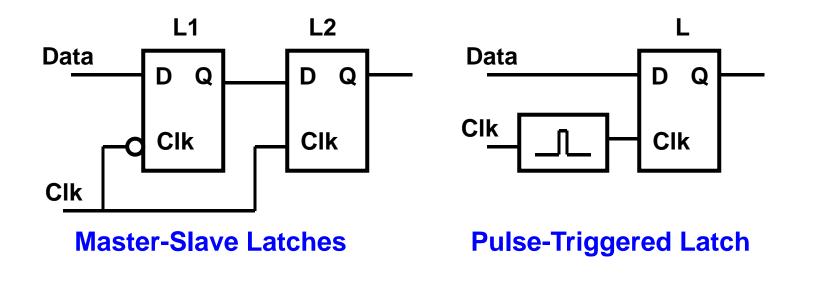

## **Pulse-Triggered Latches An Alternative Approach**

Remember: Use registers to avoid race-around problem. Two latches in cascade: master-slave Alternative: Pulse triggered latches

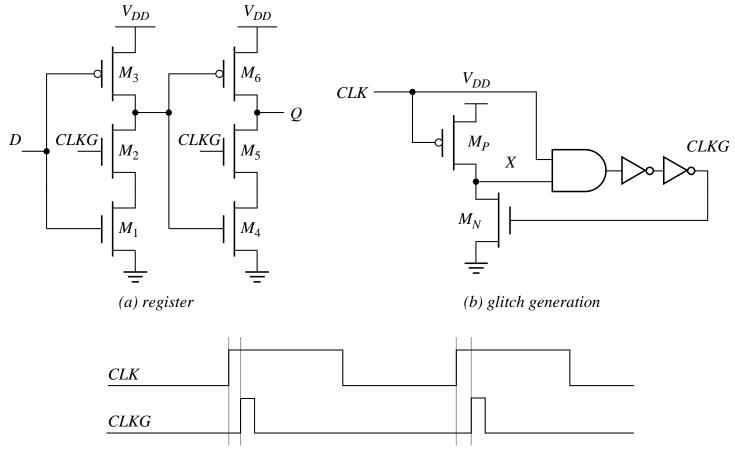

#### **Pulsed Latches**

(c) glitch clock

#### **Pulsed Latches**

#### Hybrid Latch – Flip-flop (HLFF), AMD K-6 and K-7 :

#### **Hybrid Latch-FF Timing**

## **More Topics**

- Reset and enable inputs

- Scan-enabled CSEs

- Sense-amplifier based CSEs

- Double-edge triggered

- Low-leakage sleep mode

- (Ultra) Low voltage

- Soft-error / SEU tolerance

#### Timing of CSEs

## **Summary**

#### Background

Timing, terminology, classification

#### Static CSEs

Latches

Registers

- Dynamic CSEs

- Latches

- Registers