# **Transition Probability**

$p_{A=1} = p_A$ : given probability of value of signal A being 1 in any clock cycle  $p_{A=0} = p_A$ : given probability of value of signal A being 0 in any clock cycle Note the ' prime (for inversion of signal)

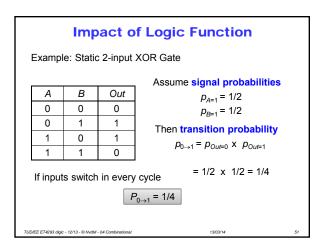

### Transition probability:

TUD/EE ET4293 digic - 12/13 - © NvdM - 04 C

Probability of 1 to 0 or 0 to 1 transition at clock edge:  $\alpha = p_A(1-p_A) = p_A p_{A'}$

13/03/14

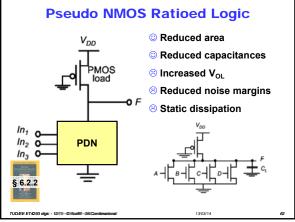

| Pseudo | NMOS | Ratioed | Logic |

|--------|------|---------|-------|

|--------|------|---------|-------|

Performance of a pseudo-NMOS inverter

| Size | V <sub>oL</sub> [V] | Power [µW] | t <sub>pLH</sub> [ps] |

|------|---------------------|------------|-----------------------|

| 4    | 0.693               | 564        | 14                    |

| 2    | 0.273               | 298        | 56                    |

| 1    | 0.133               | 160        | 123                   |

| 0.5  | 0.064               | 80         | 268                   |

| 0.25 | 0.031               | 41         | 569                   |

D/EE ET4293 digic

**Pseudo NMOS Ratioed Logic** Differential Cascode Voltage Switch Logic (DCVSL) Rail-to-rail swing No static dissipation 8 Rationed Out Cross-over currents 8 Wiring A PDN1 PDN2 в B Vss Vss

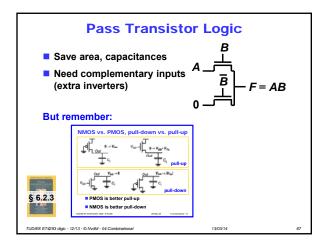

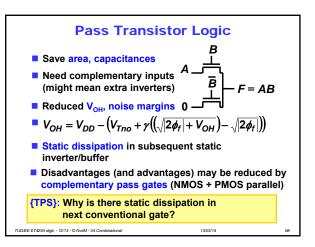

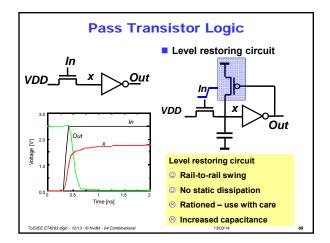

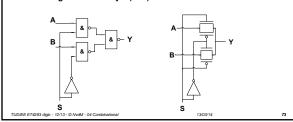

### **Pass Transistor Logic**

- Most typical use: for multiplexing, or path selecting

- Assume in circuit below it is required to either connect A or

- B to Y, under control by S

- Y = AS + BS' (S' is easier notation for S-bar = S-inverse = S)

Y = ((AS)' (BS)')' allows realization with 3 NAND-2 and 1 INV: 14 transistors

- Pass gate needs only 6 (or 8) transistors

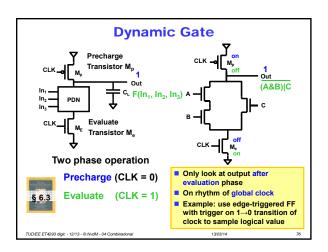

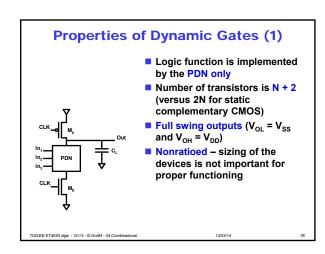

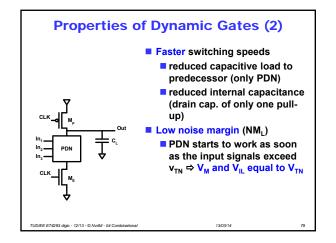

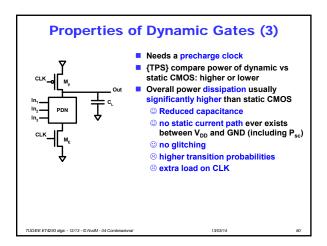

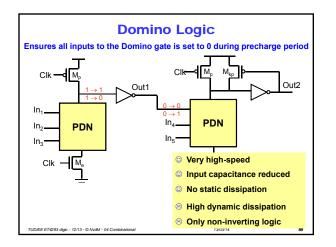

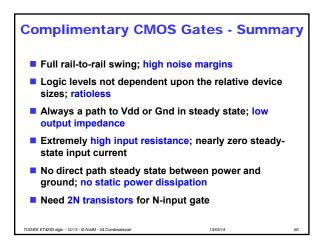

## Static vs. Dynamic CMOS Circuits

#### Static

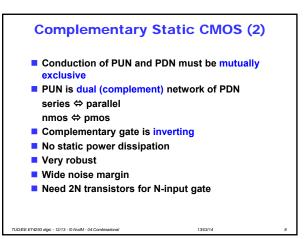

- At every point in time (except during the switching transients) each gate output is connected to either Vob or Vss via a low-resistive path.

- The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (except during switching periods)

- Require 2N transistors for N inputs (fan-in of N)

#### **Dynamic**

- Output not permanently connected to Vdd or Vss

- Output value partly relies on storage of signal values on the capacitance of high impedance circuit nodes.

**Conditions on Output**

evaluation

is stored on C<sub>L</sub>

Only one output transition per

clock cycle, after CLK  $0 \rightarrow 1$ . It

cannot be charged again until

the next precharge operation

Inputs to the gate can make at

impedance state during and

after evaluation (PDN off), state

most one transition during

Output can be in the high

- Input only active when clock is active

- Requires N+2 transistors for N inputs

E ET4293 digic - 12/13 - © NvdM - 04 Combinational

E ET4293 digic - 12/13 - © NvdM - 04 C