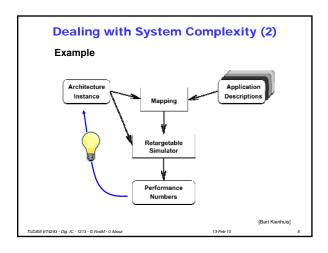

#### **More System Complexity Concepts**

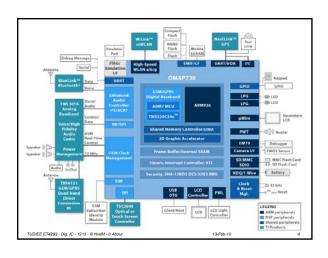

- High-level architecture design

- processors, busses, caches, cache sizes, instruction sets, IP blocks, ...

- System on chip design

- Cycle-accurate simulation

- Network-on-chip, protocols,

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

12 Eab 10

#### **Course Contents**

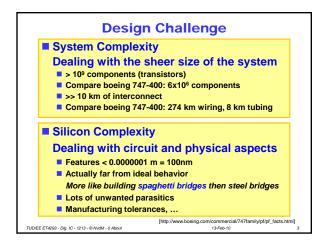

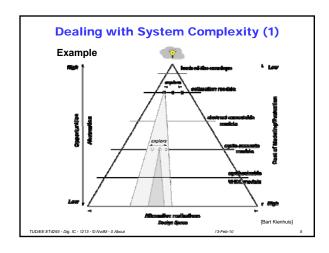

- System Complexity (Size of the system)

- This is not the focus of this course

- But this issue can't be overlooked either many of the real issues relate to the interplay of system and silicon complexity

- Silicon Complexity (circuit and physical)

- This course will focus on these aspects

- Goal is to enable design of large systems

- ... that are not wasteful of resources

- ... that work reliably in face of (almost) failing digital abstraction

- ... that can become competitive products

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

# Contents (2)

- How to realize the full potential of advanced manufacturing technologies in realizing digital circuits and systems

- Show how circuit-level techniques help improve the overall design properties

- Show how properties from physical design create opportunities (and limitations)

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

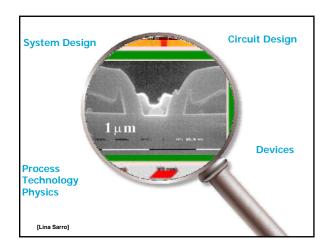

#### **Digital Electronics**

- Electronics

- Behavior of electronic circuits from an electrical perspective

- Not from an algorithmic perspective

- Digital

- Not opamps, but logic gates (etc.)

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

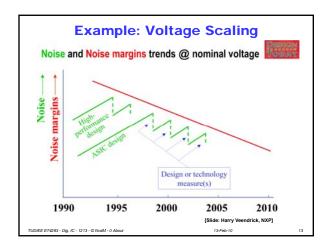

# **Digital vs Analog**

- Fundamentally, all circuits are analog, they are just 'overdriven' to achieve digital behavior

- 'Digital' is just an abstraction

- Way of looking at circuits and signals

- Understanding range of validity of digital abstraction is essential

- Deep-submicron evokes many unwanted 'analog' offerte:

- Crosstalk, delay, overshoot, reflection, supply noise, substrate noise, ...

- Digital abstraction has limited (and falling) validity

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

#### **Scaling**

- All features become smaller and smaller

- Smaller means faster but also less ideal

- Deep-submicron design becomes more like building spaghetti bridges then steel bridges

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

paris.thover.com/photos/2569.jpg www.jhu.edu/virtlab/image/MVC-007X.jpg) 12.Fo/b-10

# Why 'Electronic' insight for VLSI

- Fundamental insight in exact behavior and opportunities

- Deep scaling defeats many standard practices and abstractions

- New design issues arise

TUDIEE ET4293 - Dig. IC - 1213 - © NvdM - 0 About 13-Feb-10 14

# Why 'Electronic' insight for VLSI

- Someone needs to design and implement libraries

- Creating a model of a (standard) cell and modules requires deep understanding

- Library-based design and standard abstractions partially avoided for very high performance designs

"UD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

# Why 'Electronic' insight for VLSI

Troubleshooting

- Requires in-depth knowledge of all issues involved

- of all the circuit bugs, electrical bugs are become more prevalent, and are much harder to find, solve than logical bugs

UD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

# **Prerequisites**

- **■** Circuit Theory

- Resistor, capacitor, voltage, current, kirchoff laws, power, ...

- Digital circuits

- Boolean logic, logic gates, flip-flops, statemachines, clocking, ...

- Part 1 of the Rabaey book is essential

- MOS devices, technology, ...

- Will mostly be skipped in this course

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

#### **Course Contents**

- 1. Inverter nucleus of digital design

- Performance, robustness, area, ...

- Analysis carries over to other structures

- 2. Complex digital gates

- NOR, NAND,

- Static, dynamic,

- Sizing for speed, power

- Memory functions (flip flops)Using stored charge or using feedback

- 4. Implementation strategies

- 5. Interconnect issues

- 6. Timing design

- 7. Building blocks

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

13-Feb-10

Instructor

Dr. ir. N.P. (Nick) van der Meijs (HB 17.300) Instructor

86258 In.p.vandermeijs@tudelft.nl

(HB 17.050) A.vanLoren@tudelft.nl Lab instructor Amir Zjajo

Lucho Gutierrez (TA) Yuxin Yan (TA) available: see BB

**Guest instructors** Amir Zjajo, Edoardo Charbon

Minaksie Ramsoekh (HB 17.230) Secretary

81372 ■ M.W.S.Ramsoekh@tudelft.nl Section

Circuits and Systems http://ens.ewi.tudelft.nl/

Microelectronics & Computer Engineering Department

http://me.its.tudelft.nl

**Practice Exercises**

Transistor, Nand gate layout using Cadence

enroll for course in BB before 10PM today or your access to Cadence might be delayed.

UD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

■ Spectre Simulation exercise

Instructions next Thursday

Work in teams of 2 Need to be completed

■ Not graded

If not done already:

■ Will be checked

**Course Material**

Book:

Jan M. Rabaey - Digital Integrated Circuits, A Design Perspective, 2<sup>nd</sup> ed, Prentice Hall, 2003 (via ETV)

Web site:

http://cas.et.tudelft.nl/~nick/courses/digic

Bi-directional link with blackboard

Announcements, etc. Lecture slides (!) Project data

Blackboard Discussion Forum (!)

website

Slides / Presentation Material:

Website - published, usually after lecture, Last year's website, slides still available

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

**Project**

■ Time to Digital Converter (TDC)

A circuit that can measure time precisely, with a resolution that is smaller than a gate delay

■ TDC's have many applications

Digital Radio (instead of PLL)

■ Time resolved photon sensing

Specs and requirements still to follow

**Project Information**

■ Work with teams of 2

■ No VHDL, no layout, "just" SPECTRE, corneranalysis, ...

documentation is important

Start of project in week 3

Final presentations in week 2 of Q4 (tentatively)

(previous year's projects: Ifsr, thermometer to binary decoder, ...)

**Teams**

Make teams now

List teams, students looking for teams, next Thursday.

Completion with help from us

# **Agenda**

- Lectures on Mon 4th + 5th and Thu 7th + 8th, (EWI - room @, this room)

- Handout/web exercises, to be discussed during lecture

- Lab exercises / Design project

- Bonus points to be awarded for best designs

- Includes report and presentation

- Cadence design system

- Details will follow

- Written exam April 18, 2 pm 5 pm

- open book

- Mark determined for 50% by exam, 50% by project

- Minimum grade 5 needed for both exam and project

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

# **Agenda**

- Rest of today's lecture Chapter 3 (Devices)

- Will not be presented: Introduction - Chapter 1 Process - Chapter 2

Ch 1 - 4:

Required reading/studying for Mon Feb 18

In-class test on Chapters 1 – 4 on Mon Feb 18

TUD/EE ET4293 - Dig. IC - 1213 - © NvdM - 0 About

Questions?