### ET4293 - Virtuoso Layout Design 2012

Instructions for the layout assignment in the Course Digital IC Design ET4293

Delft University of Technology

Course Year 2011-2012

http://ens.ewi.tudelft.nl/~nick/courses/digic/

Document version: February 8, 2012

The basic steps of using the Cadence layout editor called Virtuoso will be covered. Some exercises are beneficial to gain a deeper insight into the fabrication process. This document is supposed to be a general overview of tool for beginners who haven't designed any layout before. The fundamental steps to design a PMOS device are used as an example.

Before starting, there are several things that must be set up. The following steps will guide you in this process:

### 1. Create your working directory and copy some files

>> tcsh

>> cd /home/<username>

Go to the directory where you want to create your working directory. You can select it, it's up to you!

>> cp -r /opt/cad/cadence/5.1.41/sun4v/IC5.1.41/tools.sun4v/dfII/samples/tutorials/le/cell design .

Copy *cell\_design* to the current directory and then use it as your working directory. Do not forget the "." at the end of the command line.

### >> cd ./cell\_design

Set cell\_design as your working folder. The following steps will be operated from this directory.

>> cp -r /opt/cad/cadence/5.1.41/sourceme .

>> vi sourceme

Copy *sourceme* file to your working directory and open it with vi editor. Press the 'i' key to edit it. Add the following line at the beginning of the file:

### set path = ( \$path /opt/cad/cadence/5.1/lnx86/MMSIM701/tools/bin )

1

When you are done, press 'Esc', and then type ':wq' to save the changes and leave the editor.

NOTE: You can use any kind of editors, like vim, gedit or emacs.

### >> cp /opt/cad/cadence/DesignKits/UMC090\_ET4293/designkit/display.drf .

Copy display.drf file to your working directory.

>> vi cds.lib

Open cds.lib with **vi** editor. cds.lib is an important file which specifies library information. It was copied to your project directory by the 'cp –r ... cell\_design .' command above. What we will do here is to add the library 'UMC090'. As before, press the 'i' key to edit the file and add the following line at the beginning of the file:

### include /opt/cad/cadence/DesignKits/UMC090 ET4293/designkit/cds.lib

When you are done, press 'Esc', and then type ':wq' to save the changes and leave the editor.

NOTE: You can use any kind of editors, like vim, gedit or emacs.

After following these steps, you will be ready to open the Cadence environment. Alternatively you can download the sourceme and the cds.lib files from:

http://ens.ewi.tudelft.nl/~nick/courses/digic/CadenceLocalGuide.html

### 2. Open ICFB

```

>> source sourceme

```

### >> icfb &

Now cadence is activated by the command 'icfb &' and a CDS.log window (Fig 1) pops up.

| 🙀 ictb - Log: /u/01/01/win                     | lhoos/home/qintang/CDS.log 🍥   |    | ی ک  | ۲ |

|------------------------------------------------|--------------------------------|----|------|---|

| File Tools Options                             |                                |    | Help | 1 |

| Welcome to the Cell D<br>Done with initializat | esign Tutorial qintang<br>ion. |    |      |   |

| Ι                                              |                                |    |      |   |

| mouse L:                                       | M:                             | R: |      | 1 |

| >                                              |                                |    |      |   |

Fig 1. CDS.log window of icfb

### 3. Create your library

Start "library manager" (Tools->Library Manager), then create your own library by clicking File→New→Library.

Fig 2. CDS.log window of icfb

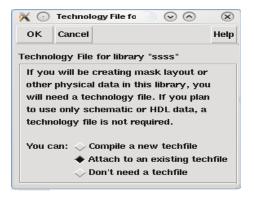

The first thing to do is to type the name of the new library ("ssss" in this example). After entering

the name and clicking OK, a new window will pop up ('Technology file' window). Select here 'Attach to an existing techfile' and press OK. Finally, you will see the following window:

| 🔀 💿 Attach Design Library to Technology File 💿 📀 🔗 |           | $\otimes$ |

|----------------------------------------------------|-----------|-----------|

| OK Cancel Defaults                                 | Apply     | Help      |

| New Design Library                                 | \$\$\$\$  |           |

| Technology Library                                 | umc90nm 🖃 |           |

Fig 3. Attach Desing Library to Tech file window

Make sure you set Technology Library to UMC090 (as in the figure above) and press OK.

### 4. Start the layout design

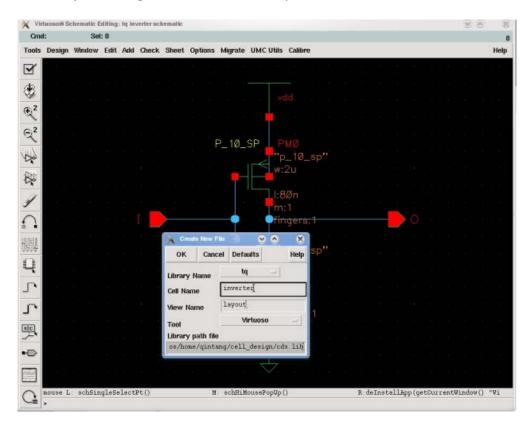

Select your library and click at: **File→New→cell view**. A new window, like the one at Fig 4, will pop up:

| Create                 | New File | <u> </u> | 8 <u>8</u> |

|------------------------|----------|----------|------------|

| ок                     | Cancel   | Defaults | Help       |

| Library N<br>Cell Nami | T        | tq 🖃     |            |

| View Nan               |          | ayout    |            |

| Tool                   |          | Virtuoso |            |

Fig 4. Create New File window

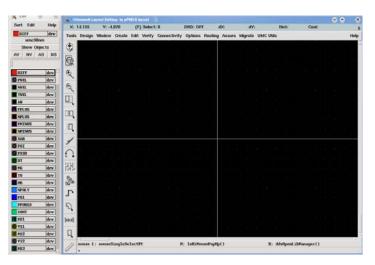

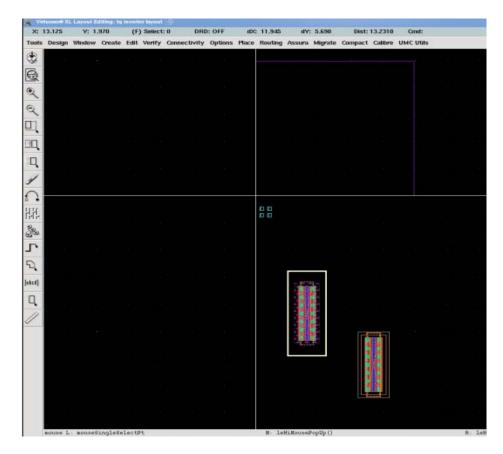

Type the cell name, and choose '**Virtuoso**' as Tool. Click OK and the Virtuoso Layout Editing window will pop up along with a **LSW** window, as shown in Fig 5. Description of various mask layers can be found at: /opt/cad/cadence/DesignKits/UMC090\_ET4293/designkit/stream.map

Fig 5. Layout Editing and LSW window

### 5. The layout design

The first thing you should do after starting the layout is fix the grid sizing. Go to **Options** $\rightarrow$ **Display**, or press the 'e' key which is the shortcut for that, and the options window (Fig 6) will pop up. The **X/Y Snap Spacing** parameter is a foundry limitation resulted from the ability to place masks on the wafer, if you make a smaller grid, probably when you check DRC of the layout you will find lots of errors about 'offgrid', if you don't correct this errors the foundry will refuse your fabrication order. The default value 0.005 is fine. Click OK to save your changes or just keep the defaults.

| 🐹 Display Opt                                                                                                                                        | lions 🕥                  |                                                                                                    |                                          |                                                                       |                  |                                       | 8    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------|------------------|---------------------------------------|------|

| OK Car                                                                                                                                               | ncel Defaults            | Apply                                                                                              |                                          |                                                                       |                  |                                       | Help |

| Display Contr                                                                                                                                        | rols                     |                                                                                                    |                                          | Grid Controls                                                         |                  |                                       |      |

| <ul> <li>Open to</li> <li>Axes</li> <li>Path Bor</li> <li>Instance</li> <li>EIP Sum</li> <li>Pin Name</li> <li>Dot Pins</li> <li>Use True</li> </ul> | Origins<br>ound<br>es    | Nets<br>Access Ed<br>Instance I<br>Array Icor<br>Label Orig<br>Dynamic I<br>Net Expre<br>Stretch H | Pins<br>15<br>Iins<br>Hillight<br>Ssions | Type 🗼 ni<br>Minor Spaci<br>Major Spaci<br>X Snap Spac<br>Y Snap Spac | ng<br>ng<br>cing | dots ⇒ li<br>1<br>5<br>0.005<br>0.005 | nes  |

| Cross Cu<br>Show Name<br>Array Displa                                                                                                                | eOf $\diamondsuit$ insta | nce 🔶 ma<br>ay Levels                                                                              | ster                                     | Filter<br>Size 6                                                      | Style            | empty                                 | _    |

| <ul> <li>♦ Full</li> <li>♦ Border</li> <li>♦ Source</li> </ul>                                                                                       | Start<br>Start           | L . X                                                                                              |                                          | Snap Modes<br>Create<br>Edit                                          |                  | ogonal<br>Angle                       |      |

| ◆ Cellview                                                                                                                                           | ⇔ Library 🗳<br>Save To   | 1                                                                                                  | ary 🔷 File<br>ad From                    | ~/.cdsenv<br>Delete Fro                                               | om               |                                       | I    |

Fig 6, Setting options for layout design

After setting up the options go back to the Virtuoso Layout Editing window (Fig 5). In the left column window, you can see the icons for Save, Fit Edit, Zoom in, Zoom out, Stretch, Copy, Move, Delete, Undo, Properties, Instance, Path, Polygon, Label, Rectangle and Ruler. You will use them frequently during designing. The short-cut keys listed below will help you work faster. Take 'r' as a case, before you draw any layer, you should select corresponding layer from the LSW palette window, click it then move the cursor to Virtuoso Layout Editing window to left-click so as to activate it. Press 'r' on the keyboard or click the icon for Rectangle, sequentially left-click and drag the mouse pointer to define the range. After drawing, *do remember to press Esc to exit this mode*. Detailed explanations for these commands are listed below.

Л

### **Edit Menu Commands**

| Rectangle          | Create a rectangle of the selected layer in the LSW.                             |

|--------------------|----------------------------------------------------------------------------------|

| Move:              | Click on any object and move it around in the layout.                            |

| Stretch:           | Click on the edge of a rectangle and size it. Be careful during using it. Before |

|                    | using it, make sure no object is selected; otherwise the selected object in your |

|                    | previous step will be moved unexpectedly.                                        |

| Path:              | Create a path of the selected layer in the LSW. (Double click to end the path).  |

| Undo:              | Undo the previous commands.                                                      |

| Сору:              | Create a copy of any object in the layout.                                       |

| <b>Properties:</b> | Change the properties of objects in the layout. Change the layer definitions and |

|                    | the changes are immediately reflected in the layout.                             |

| Instance:          | Import another existing cell view into this cell view.                           |

### Shortcuts

| - r | Create a rectangle                 | - m       | Move            |

|-----|------------------------------------|-----------|-----------------|

| - S | Stretch                            | - p       | Create path     |

| - u | Undo                               | - c       | Сору            |

| - k | Ruler                              | - q       | Show properties |

| - i | Add instance                       | - SHIFT+z | Zoom out        |

| - f | Fit the whole design on the screen | - CTRL+z  | Zoom in         |

NOTE: To zoom in/out in the schematic, use the mouse wheel.

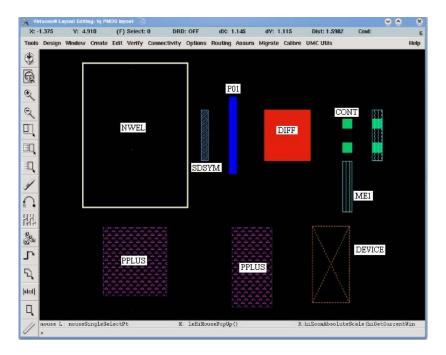

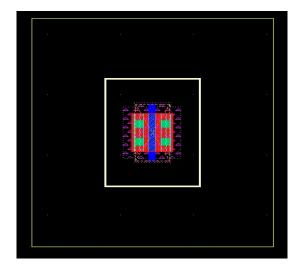

For this laboratory session our first goal is to design a PMOS transistor. PMOS transistors are built in an Nwell, which is put in the P-type substrate. The black background in **Virtuoso Layout Editing** window can be considered as the P-substrate so NMOS device can be put directly in it while PMOS devices need Nwell. Fig 7 shows the different layers required to build a PMOS transistor while Fig 8 shows a completed design. A detailed explanation of the PMOS layout design can be found in the **Appendix** section. A PMOS transistor is composed of these layers listed below (names are from LSW window):

| NWELL                  | P01 (polysilicon)                   |

|------------------------|-------------------------------------|

| PPLUS (S/D P+ implant) | CONT (contacts)                     |

| SDSYM                  | DIFF (S/D diffusion, active region) |

| DEVICE                 | ME1 (metal layer 1)                 |

| SDSYM                  | DIFF (S/D diffusion, active region) |

F

Fig 7. PMOS transistor building layers

When you're designing layout, the most important thing you should keep in your mind is the DRC rule. The design rules are specific for particular manufacturing processes, which set certain geometric and connectivity restrictions to ensure that most of design works correctly. If you don't comply with it, you will face numerous errors and warnings after DRC. That's terrible! The most frequently used rules are illustrated in **Layout\_rules.ppt**. Please read them and refer to them during designing.

Maybe you will be wondering: why there isn't any N-plus layer to connect the Nwell to a high voltage. Generally designers will design the M1-NWEL and M1-Psub contact models to connect the Nwell and substrate to metal respectively. As a result, the PMOS and NMOS models are simplified and compact.

### 6. DRC (Design Rule Checking)

DRC is available with Cadence distribution which checks most of the rules. The next step following with completing layout design is to run DRC to ensure the designed layout meets the design rules and therefore can be manufactured. There are two methods to run DRC, one is Assura and the other is Calibre. Calibre will be used in this laboratory session. However, there is no Calibre menu at the Virtuoso Layout Editing window.

In order to make it available we need to edit **.cdsinit** and **sourceme** files, so let's exit icfb, and download these two files from:

http://cobalt.et.tudelft.nl/~nick/courses/digic/CadenceLocalGuide.html

to your working directory to overwrite the old ones. Next we need to do some additional modifications:

>> cp -r /opt/cad/cadence/DesignKits/UMC090\_ET4293/designkit/RuleDecks/Calibre ..

Copy the Calibre directory to your working directory.

>> cd ../Calibre/DRC

Change to Calibre/DRC as the working directory.

>> **pwd**

This instruction shows the absolute path for our working directory (you will need it later).

>> vi G-DF-LOGIC MIXED MODE90N-1P9M2T1F-Calibre-drc-1.4-p1

Open the file using the **vi** text editor. Here we need to edit some lines to make the DRC work properly. To jump to a specific line type ":#line", where #line is the line number you want to access. Type 'i' to edit the text and press 'Esc' to stop editing. You need to edit the following lines:

• Line 291:

BEFORE: INCLUDE ./90nm\_layers\_v3.8.cal

AFTER: INCLUDE /90nm\_layers\_v3.8.cal

• Line 9238:

**BEFORE:** INCLUDE ./umc\_1P9M2T1F-X\_architecture\_Calibre-drc-V1

**AFTER:** INCLUDE <*path*>/ umc\_1P9M2T1F-X\_architecture\_Calibre-drc-V1

• Line 9246:

BEFORE: INCLUDE ./umc90N\_memory\_v14.cal

**AFTER:** INCLUDE *<path>/*umc90N\_memory\_v14.cal

Where *<path>* is the absolute path of the Calibre/DRC directory you got after typing the **pwd** command.

When you are done press 'Esc' and ':wq'.

NOTE: you can use any kind of editors, like vim, gedit or emacs.

Go back to your design directory and next execute source sourceme and restart icfb. This time you will be able to see the **Calibre** menu in your layout if you followed the steps correctly.

# Note: .cdsinit is a hidden file; you can read it by command 'cat' in x-term or set up your computer not to hide files.

Open your layout window, and select Calibre→Run DRC to invoke the Calibre Interactive

nmDRC window (Fig 9). If this is the first time for you to run DRC, click Cancel at Load Runset File (if you saved a runset file before and you want to load it, specify the runset file here). Specify DRC Rule File and DRC Run Directory as it is shown in Fig 10. The DRC Rule File can be found in the local Calibre/DRC directory. The rule file name is:

```

G-DF-LOGIC_MIXED_MODE90N-1P9M2T1F-Calibre-drc-1.4-p1

```

2. Specify the 'Top Cell' (Fig 11). If you need to change some DRC switches, you have to edit the Calibre DRC file.

|                                                                                                           | Calibre Interactive – DRC                                                                                                |      |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|

| <u>File</u> <u>T</u> ranscript                                                                            | Setup                                                                                                                    | Help |

| Bulos       Inputs       Qutpats       Run Control       Transcript       Bun <u>D</u> RC       Start RVE | Calibre-DRC Rules File<br>rules View L<br>Calibre-DRC Run Directory<br>Load Runset File<br>Runset File Path<br>OK Cancel |      |

|                                                                                                           |                                                                                                                          |      |

### Fig 9. Calibre Interactive – nmDRC window

| 💢 Calibre Interac                                                                                                                                               | ctive - nmDRC 🗿 📃 🗖 🗴                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eile Transcript                                                                                                                                                 | Setup Help                                                                                                                                               |

| Elle Transcript 3           Bules         Inputs           Qutputs         Qutputs           Run Control         Transcript           Run DRC         Start RVE | Setup Heir<br>ORC Rules File<br>G-DF-LOGIC_MIXED_MODE90IN-1P9M2T1F-Calibre-drc-1.4-p1 Uiew Load DRC Run Directory Internet/qtang/cell_design/Calibre/DRC |

|                                                                                                                                                                 |                                                                                                                                                          |

Fig 10. Specifying the DRC rule file and run directory

- Click Run DRC icon on the left of Calibre Interactive nmDRC window. Finally you will have Calibre – DRC RVE and DRC Summary Report windows with design rule violations as indicated in Fig 12 and Fig 13 respectively.

- 4. Correct your layout according to the errors and warnings in Calibre DRC RVE window (Fig 12). Click at the errors to get some information about it at the bottom of Calibre DRC RVE window (Fig 12). At the same time, the location of error will be highlighted in the layout. It should be easy for you to realize what should be modified.

- Repeat correcting layout and running DRC until there is no error shown in Calibre DRC RVE window (Fig 12). However, if there are errors like

- Minimum DIFF density over 150m\*150um area step 50 is 25%

- Maximum P+ diffusion to nearest N+ pick-up spacing is 20um

that you can ignore. The former arises because it's just a small model. The latter is due to the Nwell contact (if the PMOS model were used, there should be an Nwell-Metal contact to connect Nwell to the supply voltage).

| 🙀 Calibre Intera                           | ctive - nmDRC : to | _runset [/u/01/01/windhoos/home/qintang/ | cell_design) 🔄 😧 🔕 😵      |

|--------------------------------------------|--------------------|------------------------------------------|---------------------------|

| <u>File</u> <u>T</u> ranscript             | <u>S</u> etup      |                                          | <u>H</u> elp              |

| <u>R</u> ules<br>Inputs<br>Outputs         | Run:               | DRC (Hierarchical) -                     | _ Incremental             |

| Run <u>C</u> ontrol<br>Tr <u>a</u> nscript | File:              | PMOS_c.calibre.db                        |                           |

| Run <u>D</u> RC                            | Format:            | GDSII —                                  | Export from layout viewer |

| Start R <u>V</u> E                         | Top Cell:          | PMOS_C                                   |                           |

|                                            | 🔄 Area:            |                                          |                           |

|                                            |                    |                                          |                           |

|                                            |                    |                                          |                           |

|                                            |                    |                                          |                           |

|                                            |                    |                                          |                           |

|                                            |                    |                                          |                           |

|                                            | -                  |                                          | J                         |

|                                            |                    |                                          |                           |

Fig 11. Specifying the top cell

Fig 12. Calibre-DRC RVE window

| K DRC Summary Report - PMOS_c.drc.summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                      | 8                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>Options Windows</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |                                                             |

| RULECHECK DP_14.4.1.13D_2         RULECHECK DP_14.4.1.13E_1         RULECHECK DP_14.4.1.13E_2         RULECHECK DP_14.4.1.13E_3         RULECHECK DP_14.4.1.13E_3         RULECHECK DP_14.4.2.1.1C_1         RULECHECK DP_14.4.2.1.1C_2         RULECHECK DP_14.4.2.1.1C_2         RULECHECK DP_14.4.2.1.1D_4.2.1.1D_b1_4.2.1.1D_b2         RULECHECK DP_14.4.2.1.1D_c_1         RULECHECK DP_14.4.2.1.1D_c_2         RULECHECK DP_14.4.2.1.1D_c_1         RULECHECK DP_14.4.2.1.1D_c_1         RULECHECK DP_14.4.2.1.1D_c_1         RULECHECK DP_14.4.2.1.1D_c_1         RULECHECK DP_14.2.2.1.1E_         RULECHECK DP_14.2.2.1.1E_         RULECHECK DP_14.2.2.1.1E_         RULECHECK DP_14.2.2.1.1E_ | TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL<br>TOTAL | Res<br>Res<br>Res<br>Res<br>Res<br>Res<br>Res<br>Res<br>Res |

| RULECHECK RESULTS STATISTICS (BY CELL)<br><br>CELL PMOS c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |                                                             |

| SUMMARY<br>TOTAL CPU Time: 1<br>TOTAL REAL Time: 1<br>TOTAL Original Layer Geometries: 12 (12)<br>TOTAL DRC RuleChecks Executed: 1628<br>TOTAL DRC Results Generated: 2 (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                        | <br>2                                                       |

| Edit Row 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Col                                                                                    |                                                             |

Fig 13. DRC Summary Report

The next step is to run LVS (Layout Versus Schematic) to ensure that the schematic matches the corresponding layout. This part is not covered here.

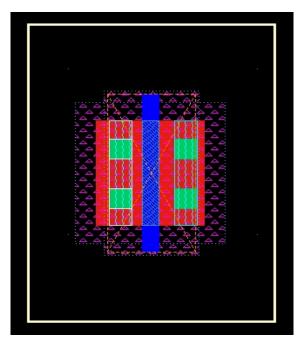

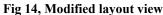

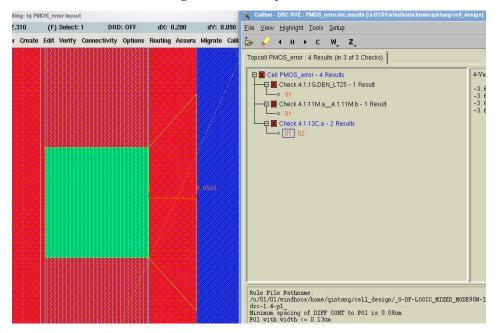

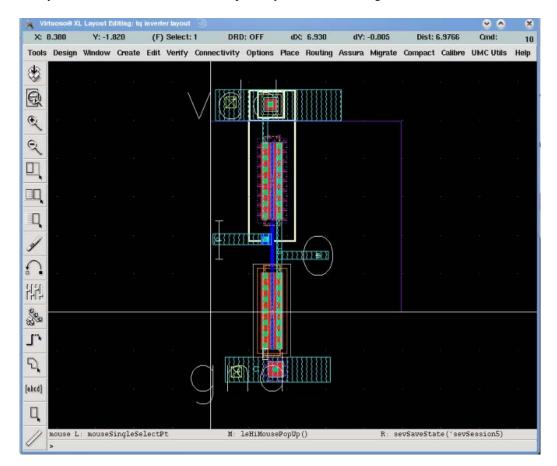

### One example to layout correction according to DRC results

This is an example to show how to correct a layout in order to make sure everything you place in the layout is compliant with the design rules. For this example, I modified the layout (Fig 14) and ran the DRC, whose results are shown in Fig 15. By clicking at **Check 4.1.13C.a-2 Results** and then double-clicking at **01**, you can see the error is highlighted and amplified in the **Layout Editing** window. The bottom of **Calibre – DRC RVE** window shows the information about the error:

Minimum spacing of DIFF CONT to P01 is 0.08um / P01 with width <= 0.13um.

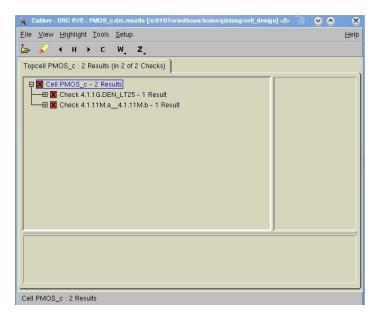

which means the CONT in the left of Poly layer is placed too close to poly, the spacing between them must be at least 0.08um. So the two CONTs on the left are supposed to be moved towards the left. Finally, after editing the layout, and running the DRC again, the results indicates that there are only two errors (Fig 16). As said previously, these two kinds of errors could be ignored.

Fig 15. Highlighted error

11

| 🙀 Calibre - DRC RVE : PMOS_c.drc.results [/u/01/01/windhoos/home/qintang/cell_design] 🐟 🍥 🧕 🙆                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <u>E</u> ile <u>V</u> iew <u>H</u> ighlight <u>T</u> ools <u>S</u> etup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>H</u> elp |

| 🦆 🖌 ∢ н → с ₩_ Z_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| Image: Control of the second state |              |

| Rule File Pathname:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |

| <pre>/u/01/01/windhoos/home/qintang/cell_design/_G-DF-LOGIC_MIXED_MODE90N-1P9M2TIF-Cal<br/>drc-1.4-p1_<br/>Minimum DIFF density over 150mX150um area step 50 is 25%</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .iore-       |

Fig 16. DRC results after correction

### 7. The design flow

When you want to design circuits, no matter how large and complicated they are, you should follow this design flow:

- 1. design the schematic

- 2. simulate the schematic to make sure the function meets the requirements

- 3. design layout

- 4. Physical verification (DRC, LVS, PEX)

- 5. Post-Layout Simulation

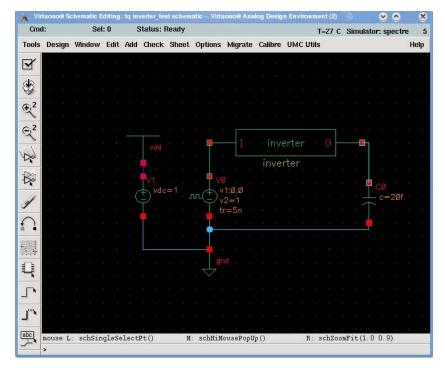

This part will introduce the first 4 steps with a simple inverter as a case. But the introduction of the forth step will focus on DRC, which has been explained in detail.

### 7.1. Design the schematic inverter.

In **CDS.log** window (Fig 1), open "library manager" (**Tools**->**Library Manager**). Click in your library and create a new cell view (**File**->**New**->**cell view**). At the "**Create New File**" window, fill in the cell name and select "**composer Schematic**" as Tool (Fig 17).

| 📉 Create          | e New File | 9       | <u> </u>  | 8       |  |  |

|-------------------|------------|---------|-----------|---------|--|--|

| ОК                | Cancel     | Defau   | lts       | Help    |  |  |

| Library N         | ame        | tq      | -         |         |  |  |

| Cell Name         | 9 i        | nverte: | ч         |         |  |  |

| View Nan          | ne s       | chemat  | iď        |         |  |  |

| Tool              | C          | ompose  | r-Schemat | lic =   |  |  |

| Library path file |            |         |           |         |  |  |

| os/home,          | /qintang   | /cell_0 | design/cd | s.libį́ |  |  |

Fig 17. Create new schematic

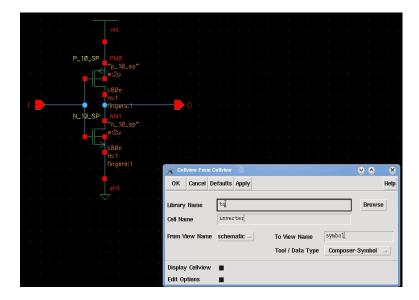

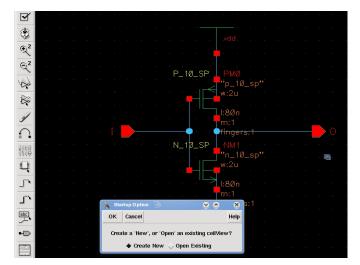

After Clicking OK, the **Virtuoso Schematic Editing** environment will show up. Press the 'i' key to add instances to the schematic and select NMOS and PMOS models from the Library UMC90 (Fig 18). Their width and length values will depend on the specific requirement. You should calculate them approximately and set these values manually.

Once the transistors are placed, select the voltage supply (Vdd) and ground (gnd) models from the **analogLib** library. Now it's time to connect them. Press the '**w**' key to connect these four models and add an input pin (**I** in this example) and an output pin (**O** in this example) by pressing the '**p**' key.

| Coheman                                  | C-11                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mos                                      | N_10_SP                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | spectre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Everything<br>Uncategorized<br>D_NOT_USE | N_10_SPI<br>N_10_SPM<br>N_10_SPM                                                                                                                                                  | al<br>Al<br>Al                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | auLvs<br>hspiceD<br>spectre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| M bipolar                                | X Add                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                | Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| J diode                                  | Library                                                                                                                                                                           | บมเc90กม <sub>ี้</sub>                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Brow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| M inductor                               | Cell                                                                                                                                                                              | Ĭ.                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |