### Write your name and student number on all pages that you submit

## Exam Digital IC Design (ET4293)

Date: Thursday, April 2, 2009 Time: 09.00 am - 12.00 am

| Student number: | Mark:           |

|-----------------|-----------------|

|                 | Student number: |

### Read first:

- Write your name and student number in the boxes above and on the odd numbered pages.

- This is an open-book exam, you can use the Rabaey book and a printed copy of the lecture slides.

- You are allowed to use a calculator.

- Circle or cross the right answer of multiple-choice.

- Write your answers on this paper in the reserved spaces. Optionally, you can hand in extra pages. Write your name and student number on these extra pages, and show on the answer sheets that more details are in the separate sheets.

- Logical inverses (Boolean negation) is identified with primes ('). (Sometimes with an overbar.)

- When you need to give an explanation or calculation, be concise but precise. In graphs, always identify and draw/write the relevant values and quantities. Pay attention to the units, and scale factors.

## Question 1.

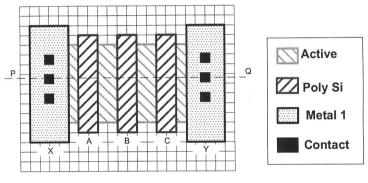

Consider the layout on the right. **a.** Draw the cross-section along the line P-Q. Clearly identify the material types.

**b.** Draw the corresponding circuit diagram (schematic). Clearly identify which nodes in the schematic correspond to the letters X, Y, A, B and C in the layout. Also identify the W/L ratios of the transistors in the schematic.

## Question 2.

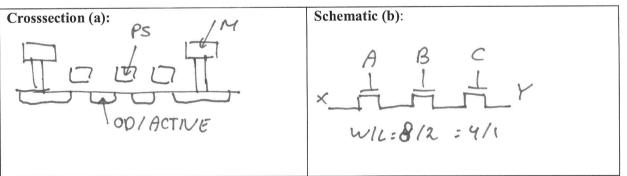

Consider the circuit on the right. Calculate  $I_D$  when  $V_{out} = 1.25$  V. Give the corresponding equation for the region of operation (do not fill in numbers) and the answer.

Assume the parameters from the inside-back cover of Rabaey. Hint: only write the equation and skip the actual calculation if you are on shortage of time.

Exam Digital IC Design (ET4293), April 2, 2009, page 1 of 6.

$$I_{D} = 157.3 \mu A$$

Equation:

$$I_{D} = k_{m} \frac{W}{L} \left( \left( V_{gs} - V_{T} \right) V_{DSAT} - \frac{V_{DSAT}}{2} \right) \left( 1 + 2 V_{DS} \right)$$

$$= 115.10^{6}.4 \left( \left( 1.25 - 0.43 \right) 0.63 - \frac{(0.63)^{2}}{2} \right) \left( 1 + 0.06 \times 1.25 \right) = 157.3 \mu A$$

### Question 3.

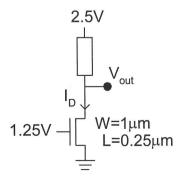

Consider the circuit on the right. It can be used as a low-swing driver. Assume the input transition time is 0, and take  $\phi_f = -0.3V$ .

**a.** Write the equations for  $V_{OH}$  and  $V_{OL}$  taking into account the body effect in both transistors. First write it using symbols, than fill in numbers. You don't need to solve the equations.

| Equation with symbols: | $V_{OH} = V_{DD} - V_{Tm}  V_{Tm} = V_{TO} + f_m \left( \sqrt{2} \phi_F \right) + \sqrt{\sigma_T} - \sqrt{\sigma_T} \phi_{Tm}$ | e)     |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|

| Equation with values:  | $V_{OH} =$                                                                                                                     |        |

| Equation with symbols  | VOL = 1UTP   VTP = VTPO + YP (V2/00-VOL - V                                                                                    | 21931) |

| Equation with values:  | $V_{OL} =$                                                                                                                     |        |

**b.** Assume the output swing is between 0.8 V and 1.7 V. To estimate the  $t_{plLH}$ , you want to compute the current delivered by the NMOS. What is (are) the operating region(s) of the NMOS transistor? Clearly give the ranges of  $V_{out}$  for each operating region that you find.

Operating regions and voltage ranges: Can't be linear, since Vgp =0 when Vgp input high. Thus: normal saturation or velocity seturation. Since Vpp-VpSqT = 2.5-0.63 = 1.87 > Vout max we have velocity saturation.

c. Assume that the average pull-up current over the full output swing is 400  $\mu$ A. Calculate  $t_{pLH.}$

Calculation:

Exam Digital IC Design (ET4293), April 2, 2009, page 2 of 6.

| Name: | Student number: |

|-------|-----------------|

|       |                 |

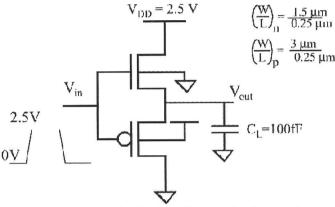

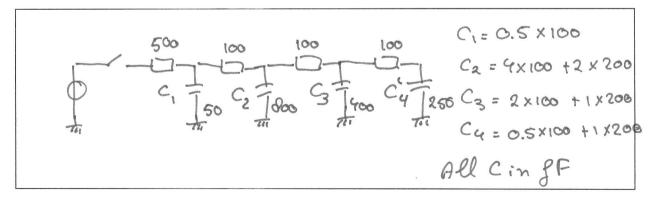

### **Question 4**.

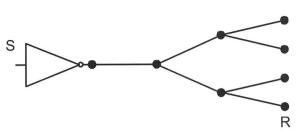

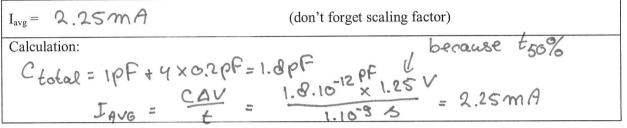

The drawing on the right schematically shows a clock-distribution network. Each one of the 7 segments (each line segment in the schematic) is 1 mm long and 1  $\mu$ m wide, and is implemented in Metal 1. Each endpoint such as R is loaded with a capacitance of 200fF. Use the technology data from the inside-back cover of the Rabaey book.

**a.** When the total capacitance of all segments together amounts to 1pF (which is not the correct answer to the next question), calculate the average current that the driver (the inverter) should deliver for a 50% delay of 1ns. For this question, please disregard the resistance of the wires. Assume  $V_{DD} = 2.5V$ .

**b.** Calculate the resistance and capacitance of *one* segment (rounding/approximation errors of about 10% are allowed – it is important to show a correct calculation procedure).

| R =              | 502                                | C= 110fF                                                       |

|------------------|------------------------------------|----------------------------------------------------------------|

| Calculati<br>R = | $\frac{1000}{1} \times 0.05 = 50 $ | C= 1000 × 30 + 2000× 40 = 0.11pF<br>T T T<br>Carea 2×6 Cfringe |

c. Now, assume that each segment has a resistance of 100  $\Omega$  and a capacitance of 100 fF (these are not the correct answers to the previous question). Also assume that the output impedance of the driver is 500  $\Omega$ , but you may ignore the output capacitance of the driver. Consider the Elmore delay formula for the delay from S to R. Draw a simple RC circuit for modeling the Elmore delay, and give the values of each R and C in the schematic. Also include the 200fF load cap at each terminal.

d. Calculate the Elmore delay for the circuit in your answer to question c.

$T_{D,R} = 385P^{5}$

Exam Digital IC Design (ET4293), April 2, 2009, page 3 of 6.

# Calculation 500 × 50 + 600 × 800 + 700 × 400 + 200 × 250 = 985000 N. 10<sup>45</sup>F = 985P3.

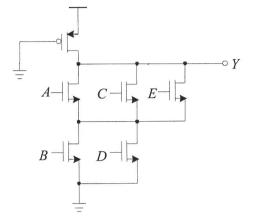

### Question 5.

Consider the circuit on the right. All NMOS transistors have the W/L ratio of 3. Assume the on-resistance for NMOS device with W/L of 1 is  $R_{on}$ .

a. What is the logic function of the output Y?

$$Y = (A + C + E) (B + D)$$

**b**.Give the input values (logic values, either 1 or 0) for the best-case and worst case pull-down resistance.

| ABCD == | 1111 | (best case) | xyxyx      | only | one y =1, others O |

|---------|------|-------------|------------|------|--------------------|

|         |      |             | worst case | 5    | 5 /                |

**c.** If the input is 11000, calculate the effective pull-down resistance. Only answer, no calculation.

$$R_{pd} = \frac{2}{3} Ron$$

## Question 6.

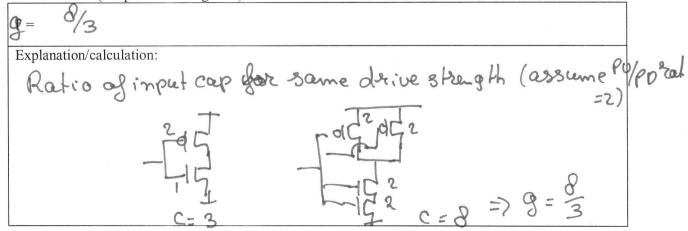

**a.** The logical effort of an inverter is 1. Determine the logical effort of a NAND-2 gate which is used as an inverter (2 inputs wired together).

Exam Digital IC Design (ET4293), April 2, 2009, page 4 of 6.

### Student number:

#### Name:

### Question 7.

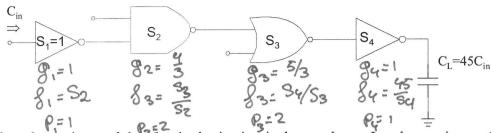

a. Calculate the optimum delay for the logic circuit shown above. Load capacitance  $C_L$  is 45 times the gate capacitance of the first inverter *Cin*. Determine the sizes S<sub>2</sub>-S<sub>4</sub> and the minimum delay expressed in term of  $t_{\nu 0}$  (intrinsic delay). Assume  $\gamma = 1$ .

### **Question 8.**

Exam Digital IC Design (ET4293), April 2, 2009, page 5 of 6.

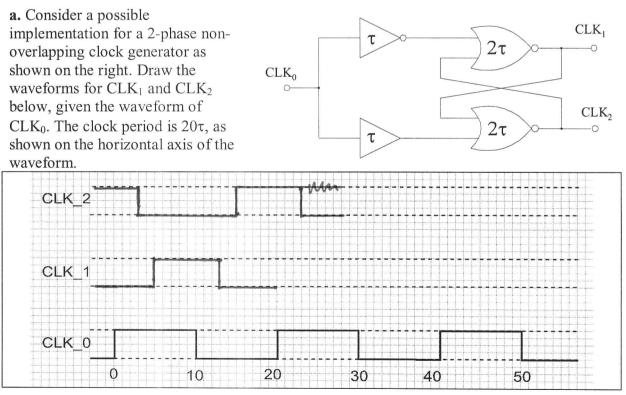

**b.** Now consider the 2 CLK2 CLK1 types of registers as shown ~ Q on the right. Determine if Dothe waveforms above are suitable to drive each of these two styles of registers. Explain your CLK1 CLK2 answer if it is negative. a: Master-slave register based on NMOS-only pass transistors CLK1 CLK2 0 °Q D CLK1 CLK2 b: Dynamic edge-triggered register Register b: Yes/No Register a: (Yes)No **Explanation:** (a) works because of data retention on (parasitic) C

Exam Digital IC Design (ET4293), April 2, 2009, page 6 of 6.